# **TECHNICAL MANUAL**

# DIRECT SUPPORT AND GENERAL SUPPORT MAINTENANCE MANUAL FOR MODEM, DIGITAL DATA MD-1002/G (NSN 5820-01-043-7646)

This copy is reprint which includes current pages from Change 1 and 2

DEPARTMENTS OF THE ARMY, THE NAVY, AND THE AIR FORCE

AUGUST 1977

### WARNING HIGH VOLTAGE is used in this equipment DEATH ON CONTACT may result if safety precautions are not observed.

115 volts ac is present within the QPSK/BPSK modem. Perform all possible maintenance with power removed. If necessary to perform operations with covers removed and power on, be extremely careful to avoid contact with high voltage.

# DON'T TAKE CHANCES!

CHANGE No 2 ARMY TM 11-5820-847-34 NAVELEX 0969-LP-169-5022 AIR FORCE TO 31R5-2G-282 C2

DEPARTMENTS OF THE ARMY, THE NAVY, AND THE AIR FORCE WASHINGTON, DC, 13 April 1982

### Direct Support and General Support Maintenance Manual MODEM, DIGITAL DATA MD-1002/G (NSN 5820-01-043-7646)

TM 11-5820-847-34/NAVELEX 0969-LP-169-50201TO 31R5-2G-282, 19 August 1977, is changed as follows:

- 1. New or changed material is indicated by a vertical bar in the margin of the page

- 2. Added or revised illustrations are indicated by a vertical bar in front of the figure caption.

- 3. Remove and insert pages as indicated below.

| Remove            | Insert                            |

|-------------------|-----------------------------------|

| i through vi      | 1 through vi                      |

| 1-1 through 1-3   | 1-1 through 1-3                   |

| 2-1 through 2-6   | 2-1 through 2-6                   |

| 2-35 and 2-36     |                                   |

| 3-1 and 3-2       | 3-1 and3-2                        |

| 3-9 through 3-14  | 3-9 through 3-14                  |

| 3-19 through 3-40 |                                   |

| 3-51 through 3-54 | -                                 |

| Figure FO-15      |                                   |

| None              |                                   |

| None              | Figure FO-32.1 (2) (Sheet 2 of 2) |

| Figure FO-40      |                                   |

| None              | Figure FO-43.1                    |

| None              | Figure FO-44.1                    |

| Figure FO-57      | Figure FO-57                      |

| 5                 | 5                                 |

4. File this change sheet in the front of the manual for future reference

By Order of the Secretaries of the Army, the Navy, and the Air Force:

Official:

ROBERT M. JOYCE Brigadier General, United States Army The Adjutant General E. C. MEYER General United States Army Chief of Staff

H.D. ARNOLD Rear Admiral, United States Navy Commander, Naval Electronic Systems Command LEW ALLEN, JR., General USAF Chief of Staff

Official:

JAMES P. MULLINS General, USAF, Commander, Air Force Logistics Command

DISTRIBUTION:

To be distributed in accordance with Special Mailing List.

TM 11-5820-847-34 NAVELEX 0969-LP-169-5020 TO 31 R5-2G-282 DEPARTMENTS OF THE ARMY,

THE NAVY, AND THE AIR FORCE

WASHINGTON. DC, 19August 1977

### DIRECT SUPPORT AND GENERAL SUPPORT MAINTENANCE MANUAL MODEM, DIGITAL DATA MD-1002/G (NSN 5820-01-043-7646)

|         |    | REPORTING ERRORS AND RECOMMENDING IMPROVEMENTS<br>You can help improve this manual. If you find any mistakes or if you kn<br>of a way to improve the procedures, please let us know. Mail your lett<br>DA Form 2028 (Recommended Changes to Publications and Blank Form<br>or DA Form 2028-2 located in back of this manual direct to: Commander,<br>Army Communications-Electronics Command, ATTN: DRSEL-ME-MQ, F<br>Monmouth, NJ 07703.<br>For Air Force, submit AFTO Form 22 (Technical Order Syst<br>Publication Improvement Report and Reply) in accordance with paragra<br>65, Section VI, T.O. 00-5-1. Forward direct to Prime ALCIMST.<br>For Navy, mail comments to the Commander, Naval Electron<br>Systems Command, ATTN: ELEX 45053 (O.H.), Washington, DC 20360<br>any case, a reply will be furnished direct to you. | ter,<br>ns),<br>US<br>fort<br>em<br>aph<br>ics |      |

|---------|----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------|------|

|         | 4  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | agraph                                         | Page |

| CHAPTER | 1. | INTRODUCTION Scope                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 1-1                                            | 1-1  |

|         |    | Equipment designators                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 1-1                                            | 1-1  |

|         |    | Differences in equipment                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 1-2                                            | 1-3  |

|         | 2. | FUNCTIONING OF EQUIPMENT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 1-5                                            | 1-5  |

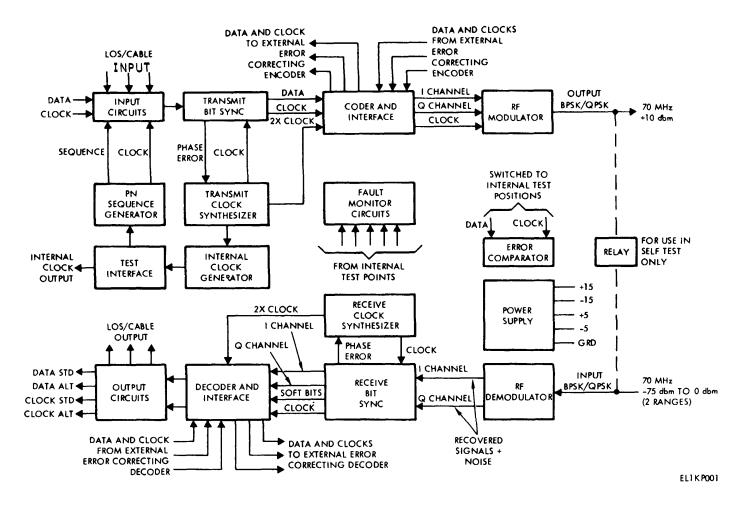

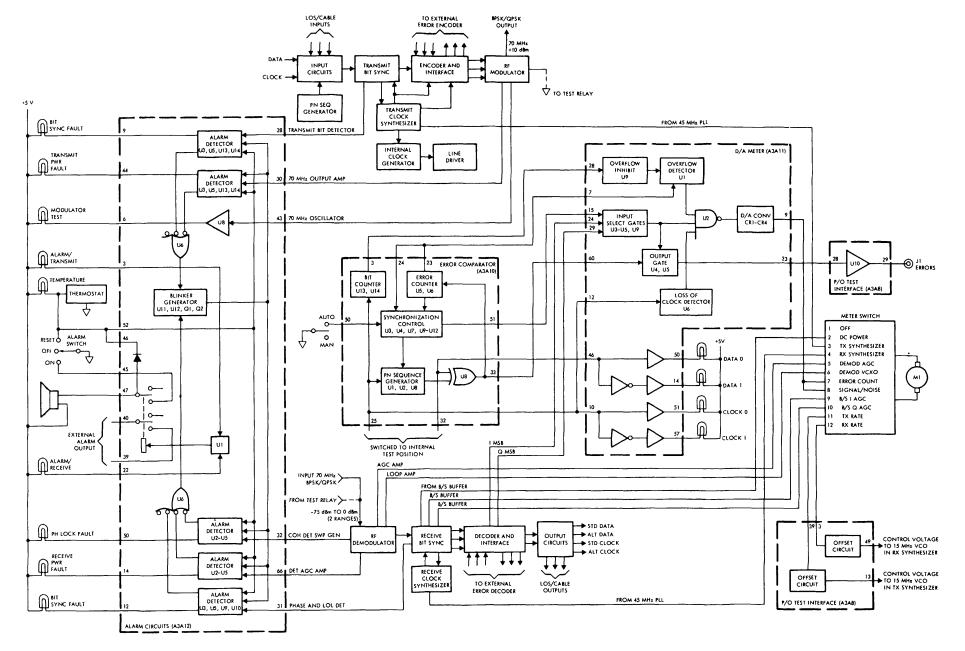

|         |    | General                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 2-1                                            | 2-1  |

|         |    | Functional description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 2-2                                            | 2-1  |

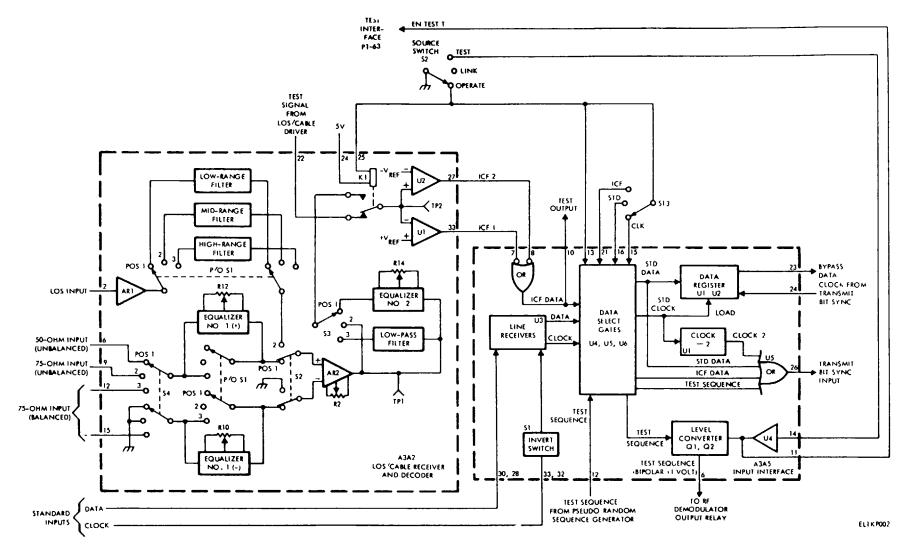

|         |    | Input circuits                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 2-3                                            | 2-4  |

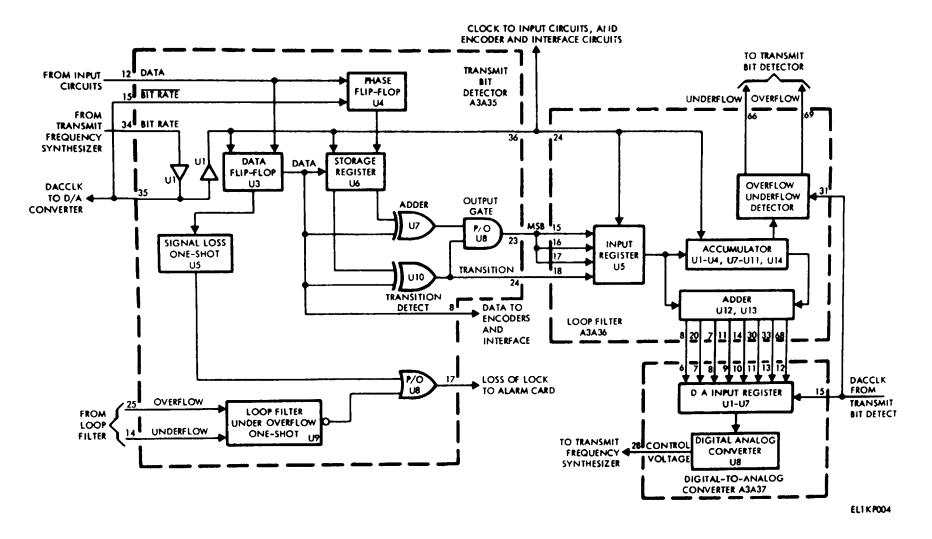

|         |    | Transmit bit synchronizer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 2-4                                            | 2-7  |

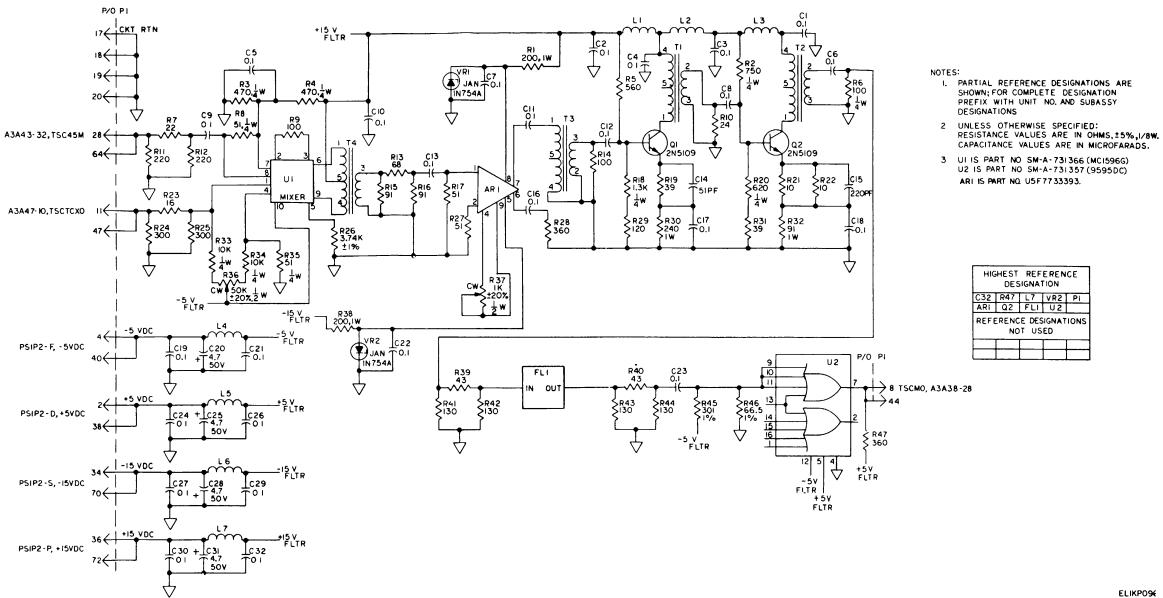

|         |    | Frequency synthesizer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 2-5                                            | 2-11 |

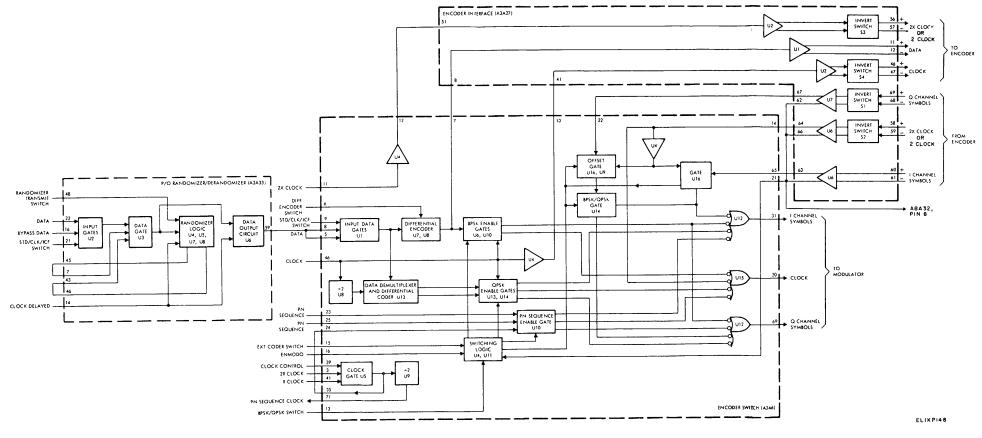

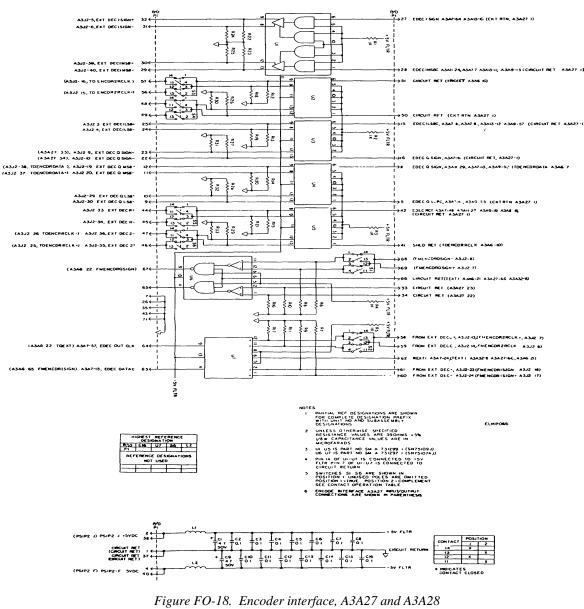

|         |    | Encoder and interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 2-6                                            | 2-21 |

|         |    | RF modulator                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 2-7                                            | 2-23 |

|         |    | RF demodulator                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 2-8                                            | 2-26 |

|         |    | Receive bit synchronizer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 2-9                                            | 2-42 |

|         |    | Receive frequency synthesizer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 2-10                                           | 2-47 |

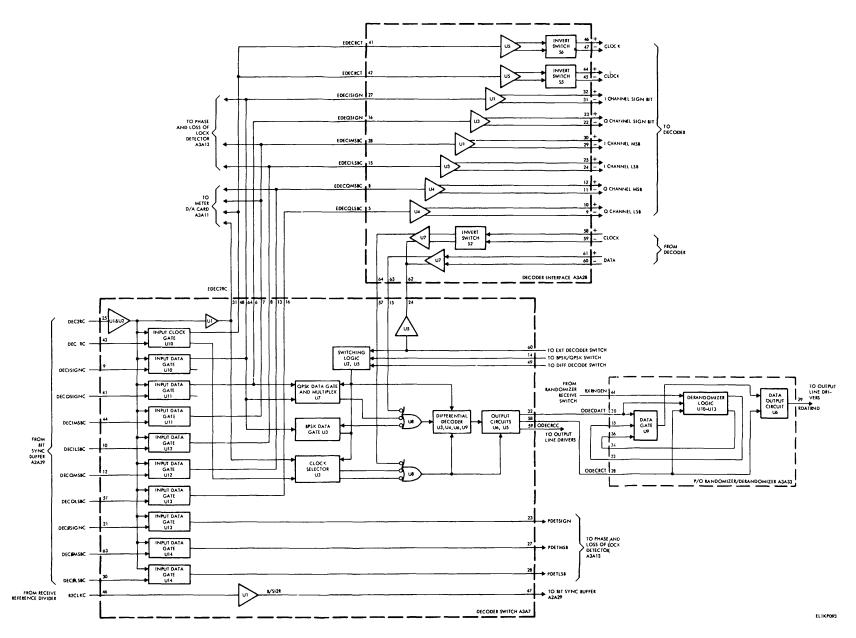

|         |    | Decoder and interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 2-11                                           | 2-47 |

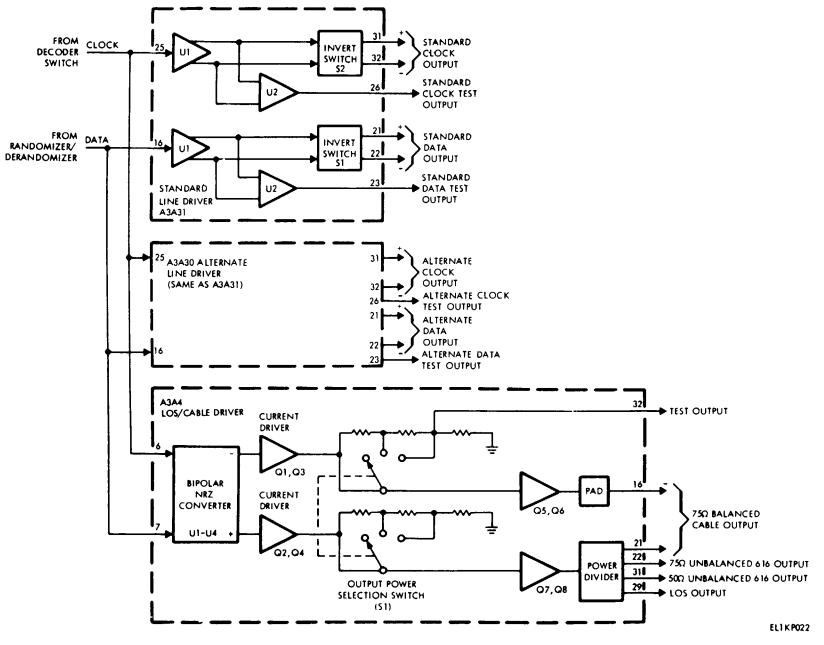

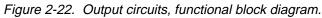

|         |    | Output circuits                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 2-12                                           | 2-50 |

|         |    | Internal clock generator                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 2-13                                           | 2-52 |

|         |    | Test and monitor functions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 2-14                                           | 2-53 |

| CHAPTER | 3. | MAINTENANCE INSTRUCTIONS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                |      |

| SECTION | Ι. | Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                |      |

|         |    | General                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 3-1                                            | 3-1  |

|         |    | Tools, test equipment, and material required for maintenance                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 3-2                                            | 3-1  |

|         |    | Preventive maintenance                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 3-3                                            | 3-1  |

Change 2 i

TECHNICAL MANUAL No 11-5820-847-34 TECHNICAL MANUAL NAVELEX 0969-LP-169-5020 TECHNICAL ORDER No 31R5-2G-282

# TM 11-5820-847-34/NAVELEX 0969-LP-169-5020/TO 31R5-2G-282 Paragraph Page

|          |      |                                                                            |        | raye         |

|----------|------|----------------------------------------------------------------------------|--------|--------------|

|          |      | Operational checks                                                         |        | 3-2<br>3-2   |

| SECTION  | ١١.  | Cleaning<br>Modem Troubleshooting                                          |        | 3-2          |

| SECTION  | п.   |                                                                            |        | 3-2          |

|          |      | General Troubleshooting procedure                                          |        | 3-2          |

|          |      | •                                                                          |        | 3-2          |

|          |      | Self-test procedure Corrective actions                                     |        | 3-3<br>3-5   |

|          |      | Chassis and card file fault isolation                                      | . 3-9  | 3-5          |

|          | III. | Modem Alinement and Repair                                                 | . 3-10 | 5-17         |

|          |      | Adjustment and alinement procedures                                        | . 3-11 | 3-19         |

|          |      |                                                                            |        | 3-19<br>3-19 |

|          |      | Power supply adjustment                                                    |        | 3-19         |

|          |      | Stable clock adjustment<br>Transmit frequency synthesizer alinement        |        | 3-19         |

|          |      |                                                                            |        | 3-21         |

|          |      | Receive frequency synthesizer alinement                                    |        | 3-22         |

|          |      | Modulator output power adjustment                                          |        | 3-23         |

|          |      | Demodulator AGC level adjustment                                           | . 3-17 |              |

|          |      | Post multiplier AGC level adjustment                                       |        | 3-26         |

|          |      | Demodulator acquisition threshold Adjustment                               |        | 3-26         |

|          |      | Deleted                                                                    |        | 3-29         |

|          |      | Demodulator phase adjustment                                               |        | 3-29         |

|          |      | Receive bit synchronizer alinement                                         |        | 3-31         |

|          |      | Deleted                                                                    |        | 3-36         |

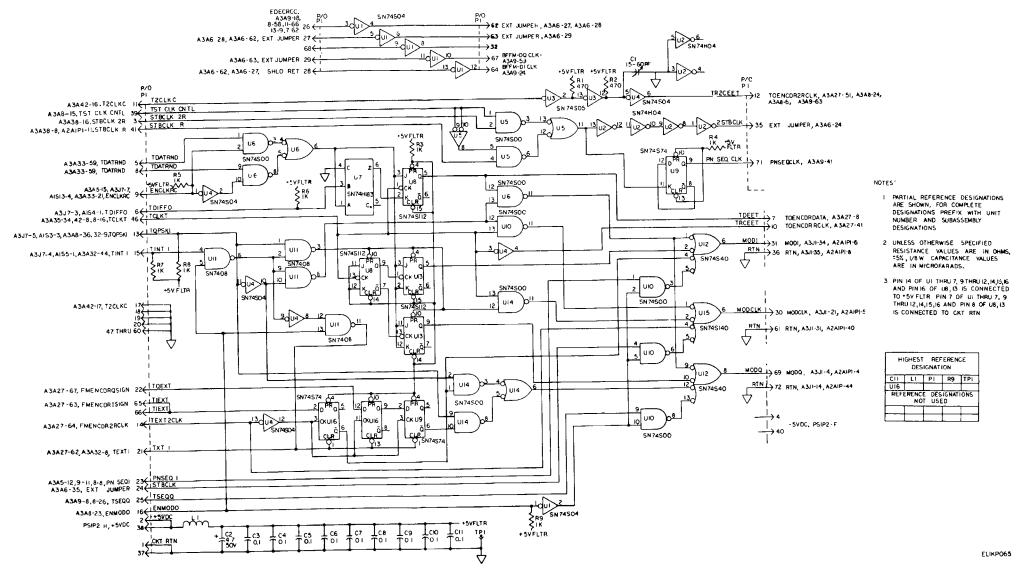

|          |      | Encoder switch timing alinement                                            | . 3-24 | 3-36         |

|          |      | Receive bit synchronizer alarm threshold alinement                         | . 3-25 | 3-36         |

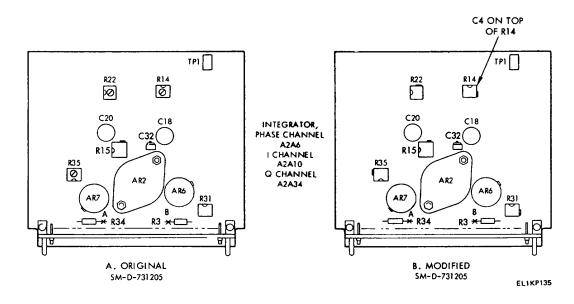

|          |      | Phase control integrator A2A6, abbreviated alinement                       | . 3-26 | 3-37         |

|          |      | Phase control integrator A2A10, abbreviated alinement                      | . 3-27 | 3-38         |

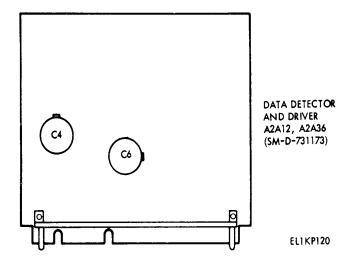

|          |      | Data detector and driver (A2A12IA2A36) abbreviated alinement               | . 3-28 | 3-41         |

|          |      | Phase adjust and detector drive (A2A14) abbreviated alinement              |        | 3-41         |

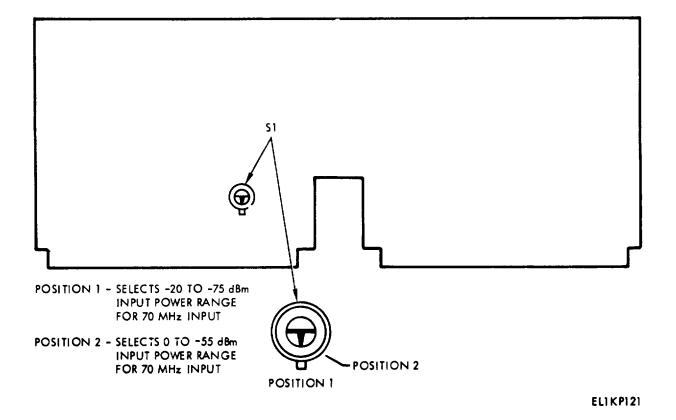

|          |      | 70-MHz, gain control amplifier A2A16, abbreviated alinement                |        | 3-42         |

|          |      | Coherent detector and AGC loop amplifier (A2A19), abbreviated alinement    |        | 3-42         |

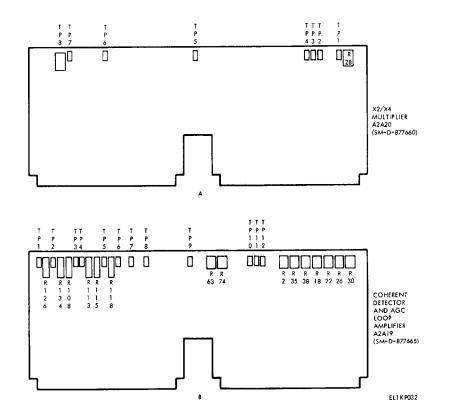

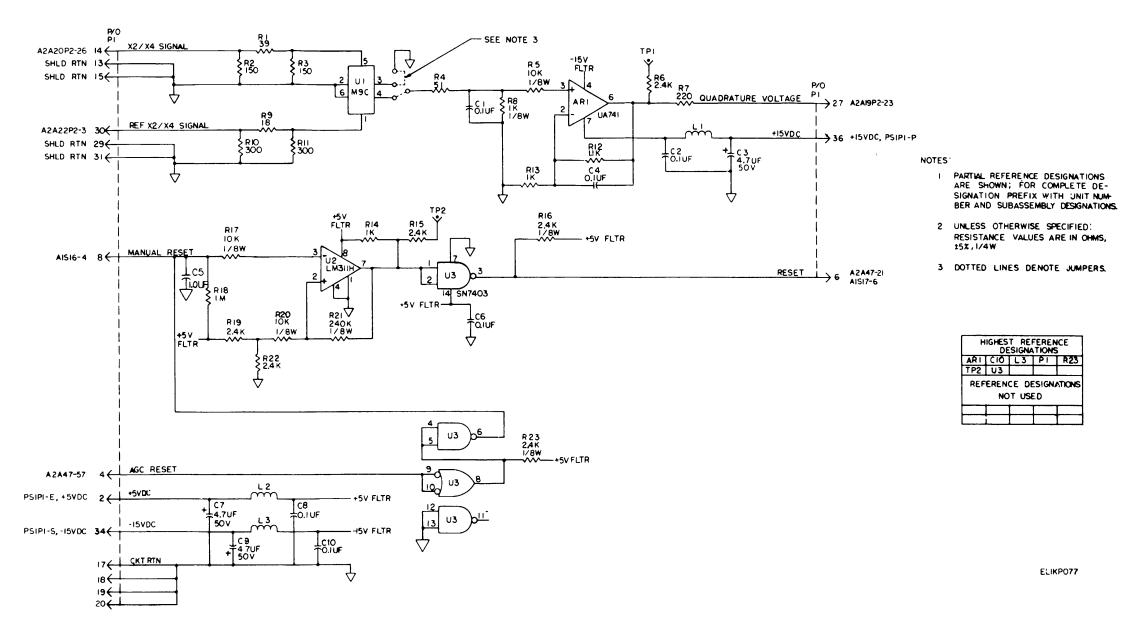

|          |      | X2/X4 multiplier (A2A20), abbreviated alinement                            |        | 3-43         |

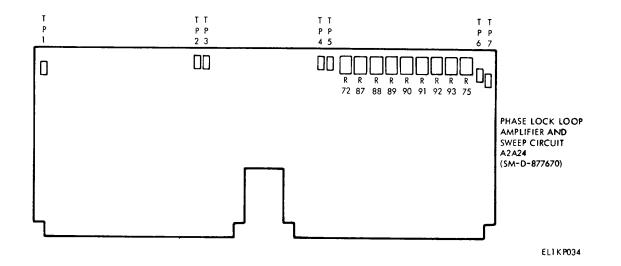

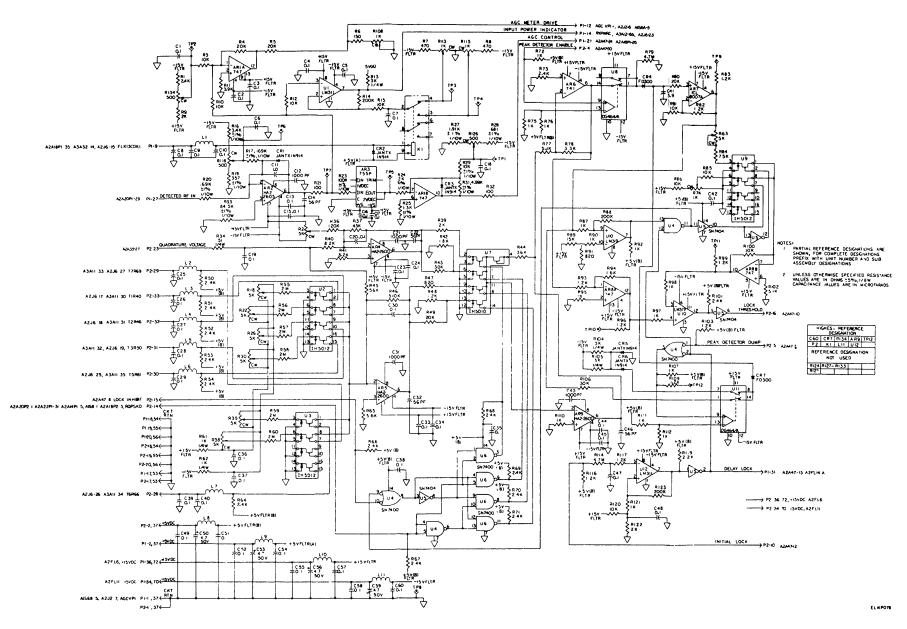

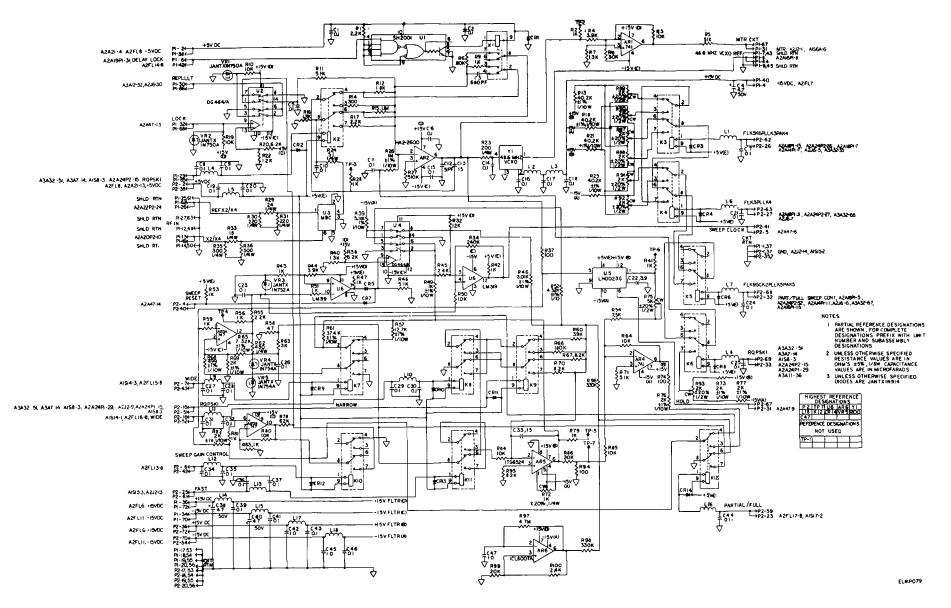

|          |      | Phase lock loop amplifier and sweep circuit (A2A24), abbreviated alinement |        | 3-44         |

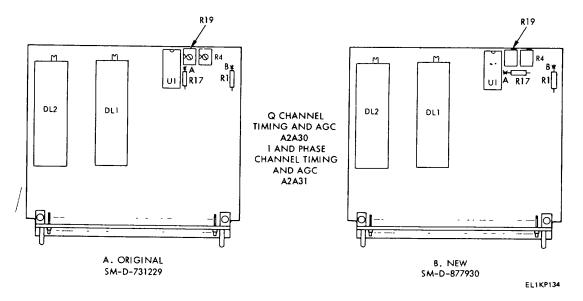

|          |      | Timing and AGC (A2A30, A2A31), abbreviated alinement                       |        | 3-44         |

|          |      | Phase control integrator A2A34, abbreviated alinement                      |        | 3-44         |

|          |      | Stable clock (A3A39), abbreviated alinement                                |        | 3-45         |

|          |      | Removal and replacement procedures                                         | . 3-37 | 3-45         |

|          | IV.  | Performance Test Procedures                                                |        |              |

|          |      | Performance testing                                                        |        | 3-46         |

|          |      | Performance failure analysis                                               |        | 3-49         |

|          |      | Assembly location                                                          | . 3-40 | 3-54         |

| CHAPTER  | 4.   | GENERAL SUPPORT MAINTENANCE INSTRUCTIONS                                   |        |              |

|          |      | Scope of general support maintenance                                       | . 4-1  | 4-1          |

|          |      | Tools and test equipment                                                   | . 4-2  | 4-1          |

|          |      | Procedures                                                                 | . 4-3  | 4-1          |

|          | 5.   | QPSK/BPSK MODEM POWER SUPPLY DESCRIPTION AND MAINTENANCE IN-               |        |              |

|          |      | STRUCTIONS                                                                 |        |              |

| SECTION  | I.   | General Description                                                        |        |              |

|          |      | General                                                                    | . 5-1  | 5-1          |

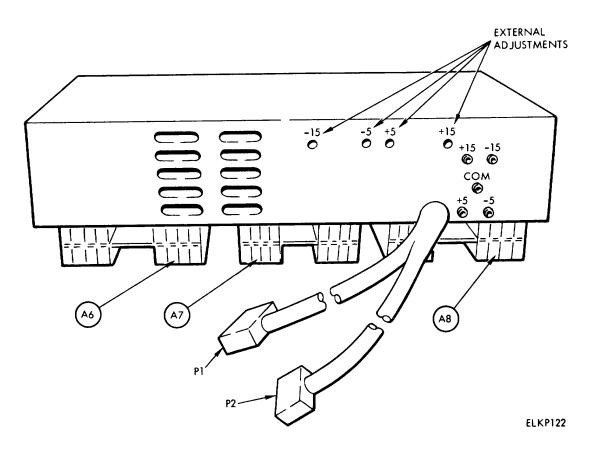

|          |      | Physical characteristics                                                   | . 5-2  | 5-1          |

|          |      | Electrical characteristics                                                 | . 5-3  | 5-2          |

|          | II.  | Functional Description                                                     |        |              |

|          |      | General                                                                    | . 5-4  | 5-3          |

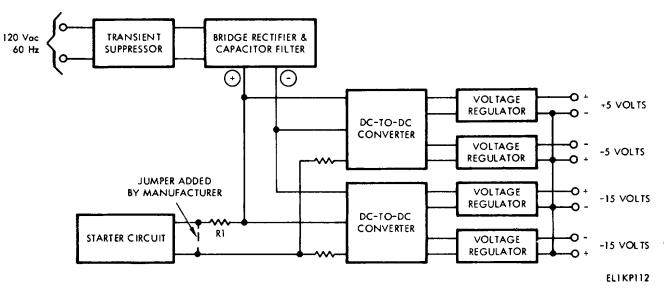

|          |      | Block diagram description                                                  |        | 5-3          |

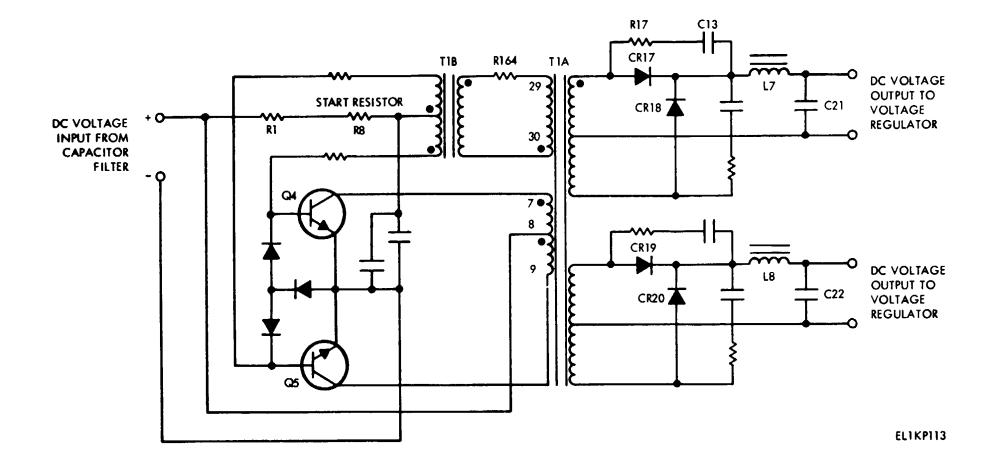

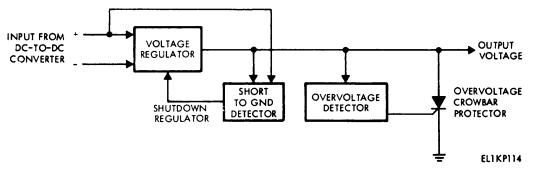

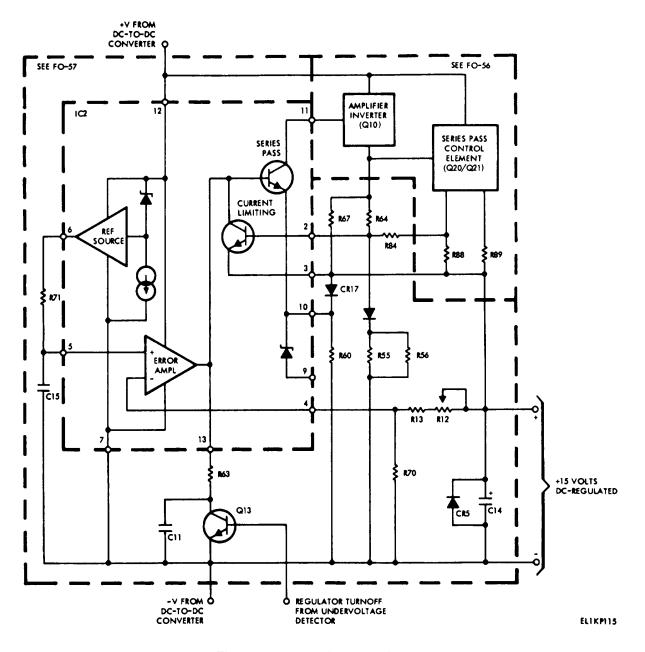

|          |      | Circuit description                                                        |        | 5-4          |

|          | III. | Direct Support Maintenance Instructions                                    |        |              |

|          |      | General                                                                    | . 5-7  | 5-9          |

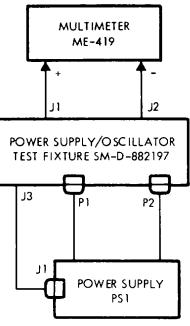

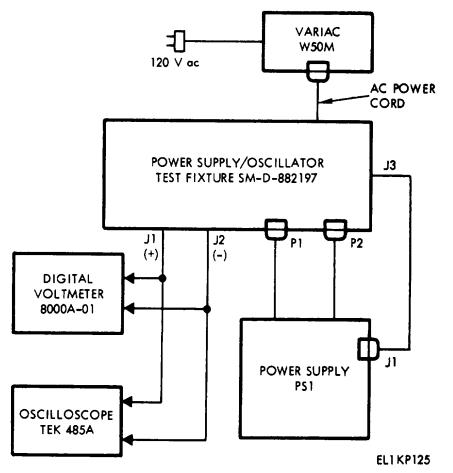

|          |      | Tools and test equipment                                                   |        | 5-9          |

|          |      | Performance testing                                                        |        | 5-9          |

|          |      | Troubleshooting                                                            |        | 5-12         |

|          |      | Removal and replacement procedures                                         |        | 5-12         |

| APPENDIX | Α.   | REFERENCES                                                                 |        | A-1          |

|          | В.   | GLOSSARY OF TERMS                                                          |        | B-1          |

|          | С.   | POWER SUPPLY PS1 WIRE LIST                                                 |        | C-1          |

|          | 0.   |                                                                            | •      | 51           |

Change2 ii

# TM 11-5820-847-34/NAVELEX 0969-LP-169-5020/TO 31R5-2E282 LIST OF ILLUSTRATIONS

|                                        | LIST OF ILLUSTRATIONS                                                                                                                                                        |

|----------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Fig No.                                | Title                                                                                                                                                                        |

| 2-1                                    | QPSK/BPSK modem, functional block diagram                                                                                                                                    |

| 2-2                                    | Input circuits, functional block diagram                                                                                                                                     |

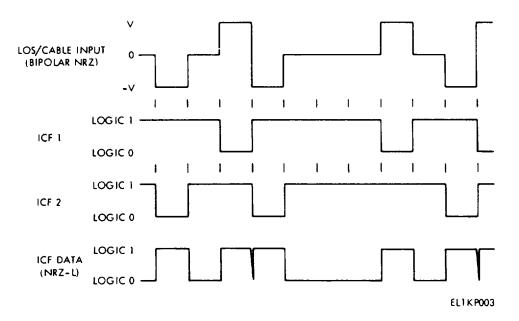

| 2-3                                    | Bipolar NRZ to NRZ conversion                                                                                                                                                |

| 2-4                                    | Transmit bit synchronizer, functional block diagram                                                                                                                          |

| 2-5                                    | Transmit bit detector, timing diagram                                                                                                                                        |

| 2-6                                    | Loop filter, functional block diagram                                                                                                                                        |

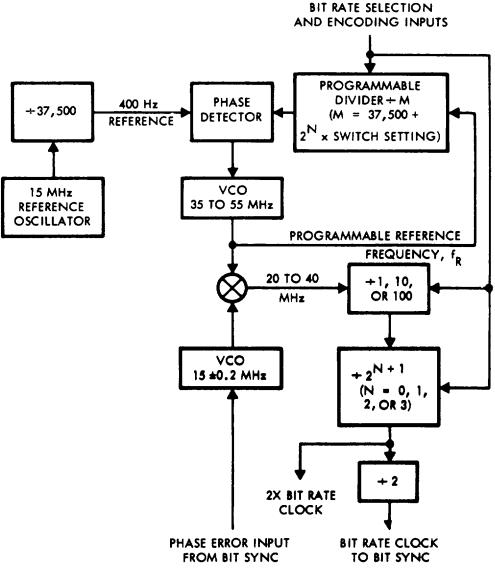

| 2-7                                    | Frequency synthesizer, general block diagram                                                                                                                                 |

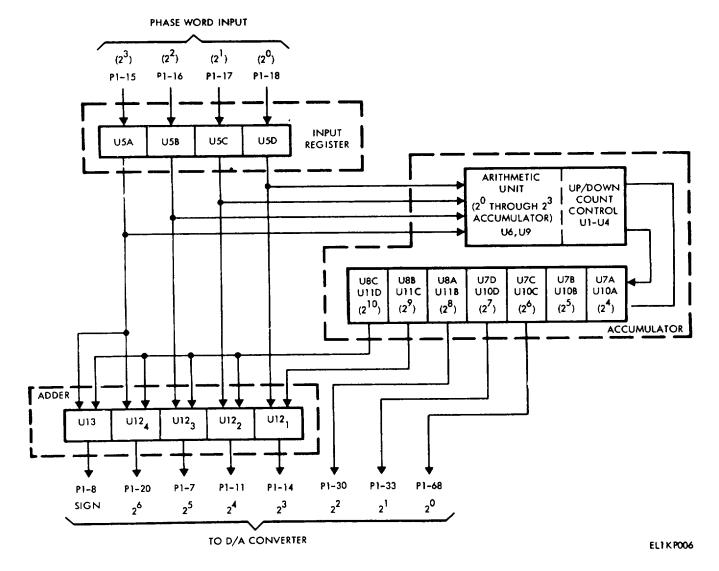

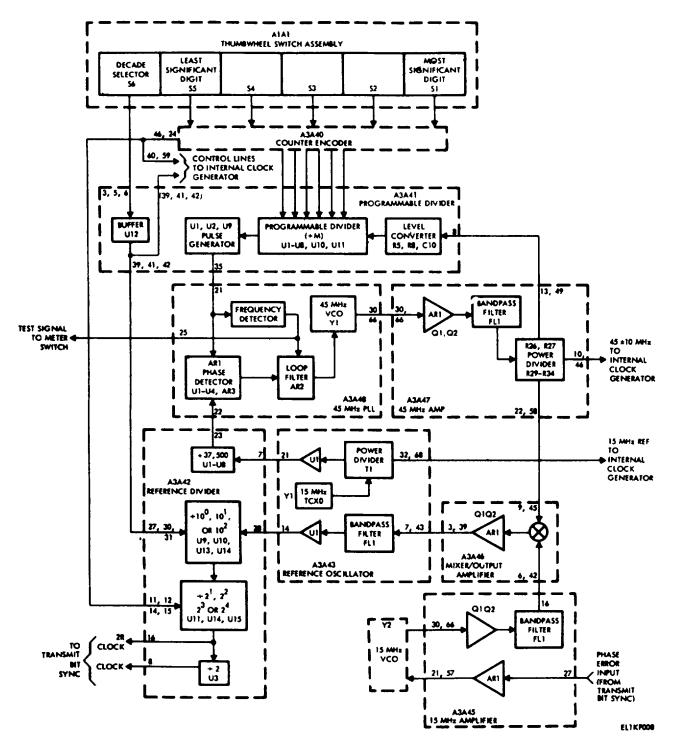

| 2-8                                    | Frequency synthesizer, functional block diagram                                                                                                                              |

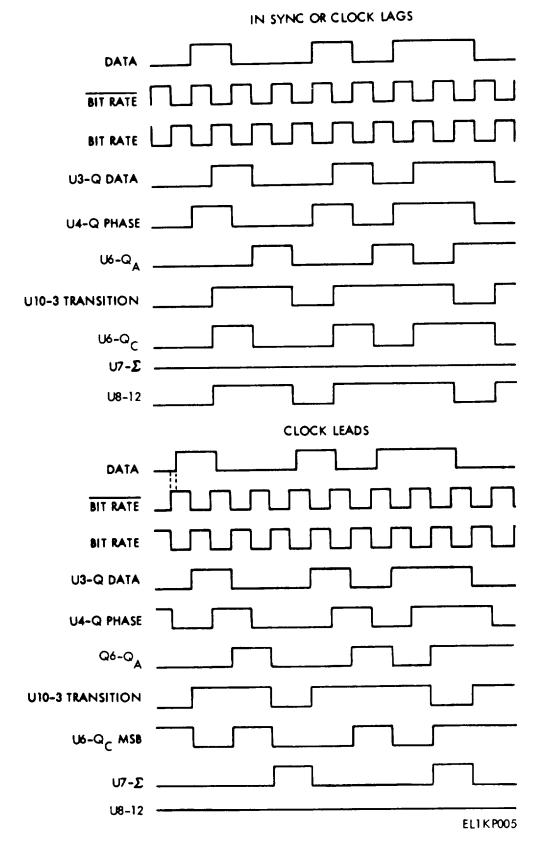

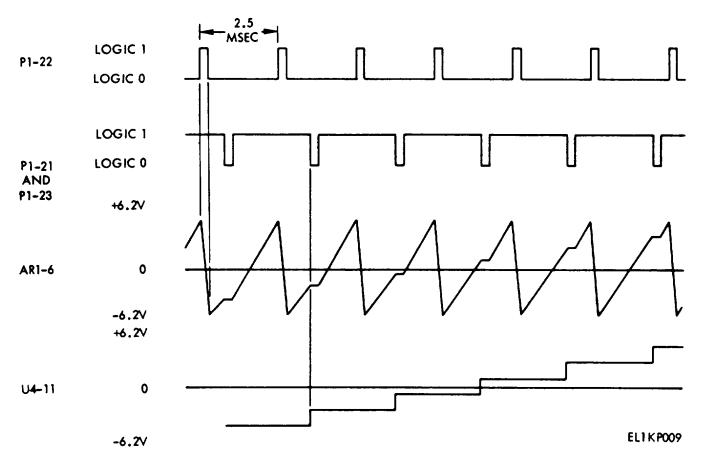

| 2-0                                    | Synthesizer phase detector, timing diagram                                                                                                                                   |

|                                        | Synuresizer phase detector, uning diagram                                                                                                                                    |

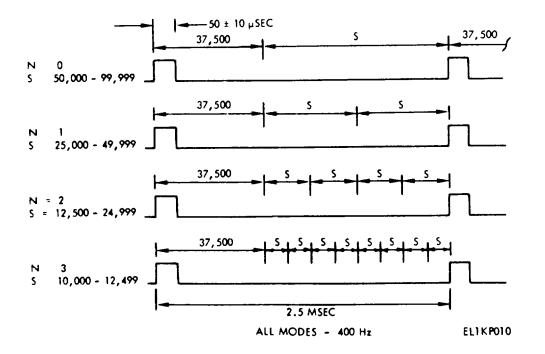

| 2-10                                   | Counter divide by 37,500 + 2N X switch setting modes                                                                                                                         |

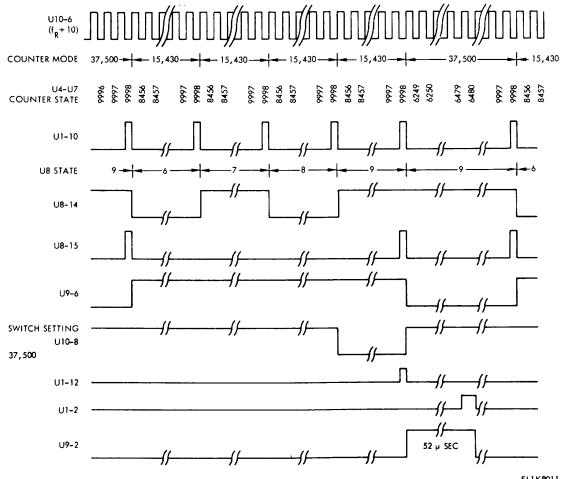

| 2-11                                   | Programmable divider, timing diagram                                                                                                                                         |

| 2-12                                   | Encoder Interface output                                                                                                                                                     |

| 2-13                                   | Data receiver and modulator timing diagram                                                                                                                                   |

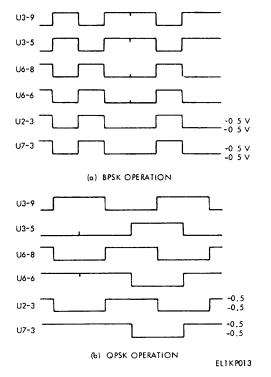

| 2-14                                   | Modulation waveforms for BPSK operation                                                                                                                                      |

| 2-15                                   | Modulation waveforms for QPSK operation                                                                                                                                      |

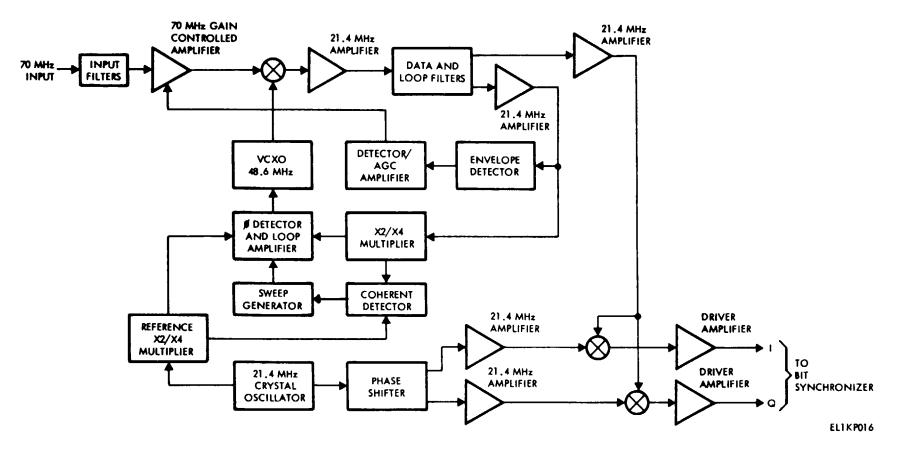

| 2-16                                   | RF demodulator, general block diagram                                                                                                                                        |

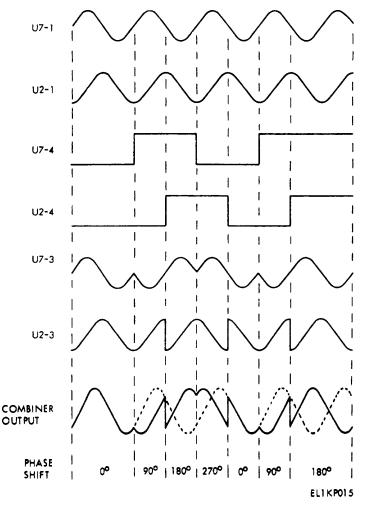

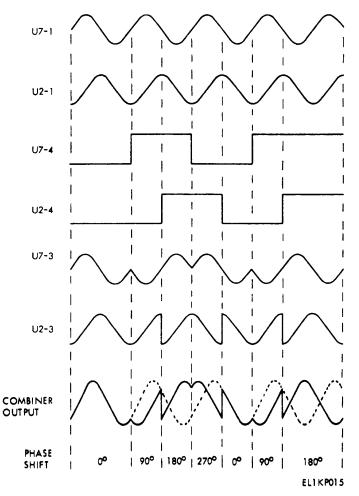

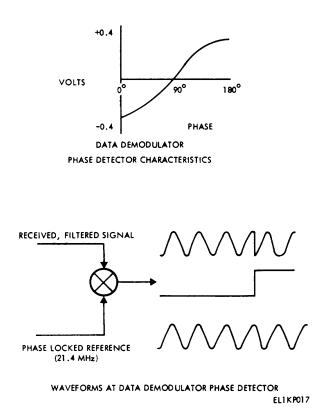

| 2-17                                   | Data detector demodulation waveforms                                                                                                                                         |

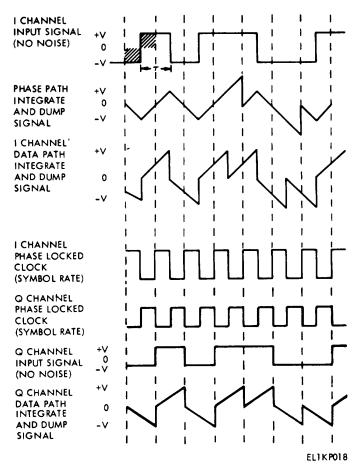

| 2-18                                   | Receive bit synchronizer waveforms                                                                                                                                           |

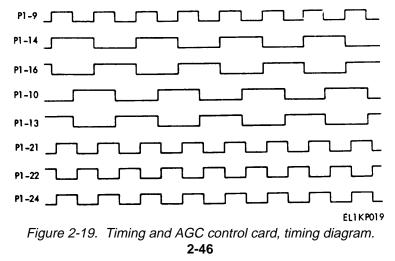

| 2-19                                   | Timing and AGC control card, timing diagram                                                                                                                                  |

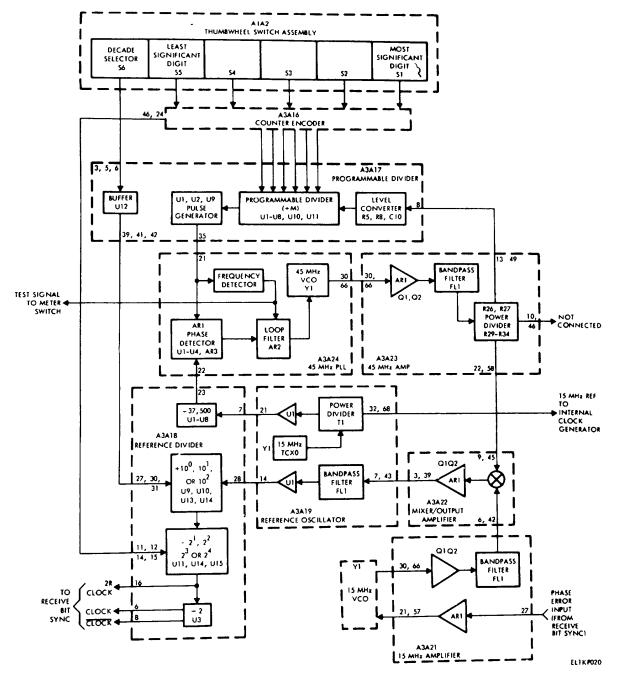

| 2-20                                   | Receive frequency synthesizer, functional block diagram                                                                                                                      |

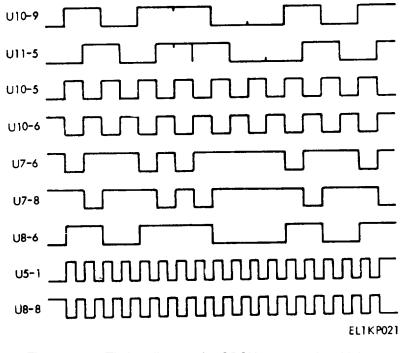

| 2-21                                   | Timing diagram for QPSK gates and multiplexer                                                                                                                                |

| 2-21                                   | Output circuits, functional block diagram                                                                                                                                    |

|                                        |                                                                                                                                                                              |

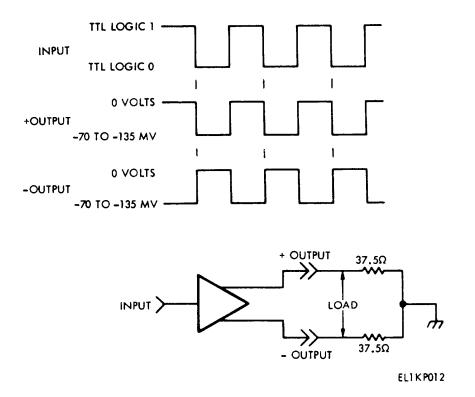

| 2-23                                   | LOS/cable driver, timing diagram                                                                                                                                             |

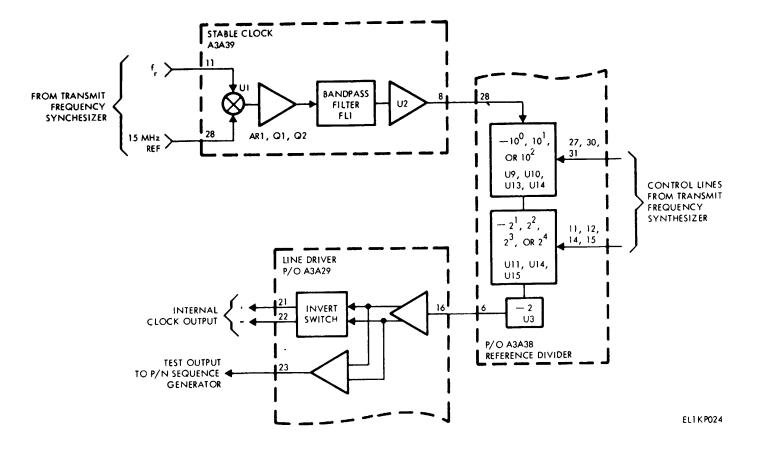

| 2-24                                   | Internal clock generator, functional block diagram                                                                                                                           |

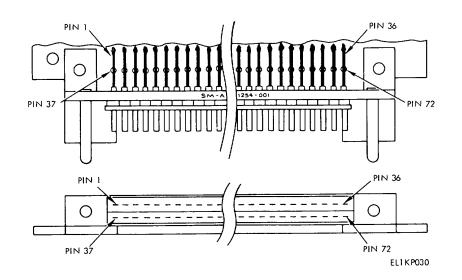

| 3-1                                    | Typical card pin locations                                                                                                                                                   |

| 3-2                                    | Reference oscillator adjustment location                                                                                                                                     |

| 3-3                                    | 45-MHz amplifier adjustment location                                                                                                                                         |

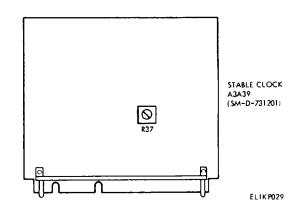

| 3-4                                    | Stable clock adjustment location                                                                                                                                             |

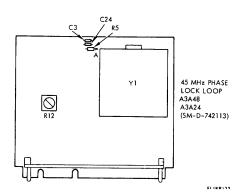

| 3-5                                    | 45-MHz phase lock loop adjustment                                                                                                                                            |

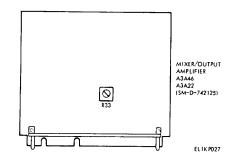

| 3-6                                    | Mixer/output amplifier adjustment location                                                                                                                                   |

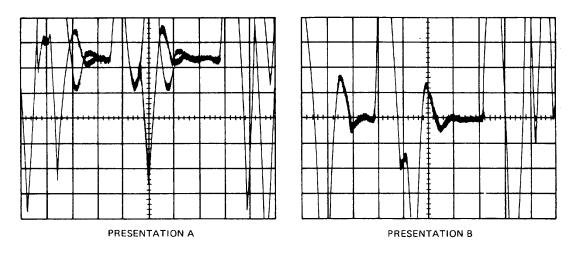

| 3-6.1                                  | Transmit frequency synthesizer adjustment waveforms                                                                                                                          |

| 3-7                                    | Modulator output power adjustment location                                                                                                                                   |

| 3-8                                    | X2/X4 multiplier and coherent detector and AGC loop amplifier, test points and adjustment location                                                                           |

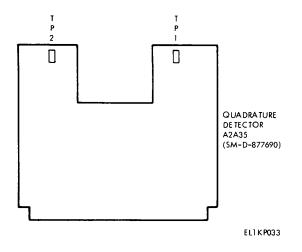

| 3-9                                    | Quadrature detector, test point location                                                                                                                                     |

| 3-10                                   | Phase lock loop amplifier and sweep circuit, test points and adjustment locations                                                                                            |

| 3-10                                   | Deleted                                                                                                                                                                      |

| -                                      |                                                                                                                                                                              |

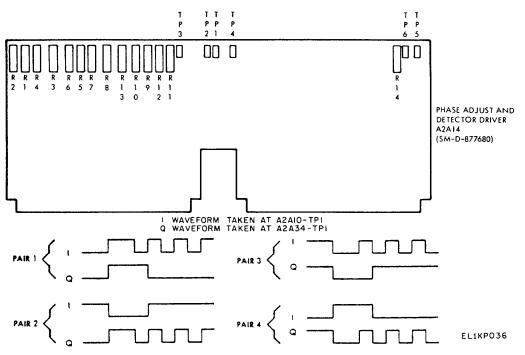

| 3-12                                   | Phase adjust and detector driver, test points adjustment locations and waveforms                                                                                             |

| 3-13                                   | Timing and AGC, test points and adjustment locations                                                                                                                         |

| 3-14                                   | Integrator, test points and adjustment locations                                                                                                                             |

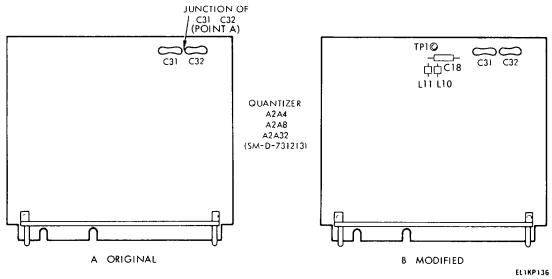

| 3-15                                   | Quantizer, test points and adjustment locations                                                                                                                              |

| 3-15.1                                 | Filter bandwidth adjustment waveforms                                                                                                                                        |

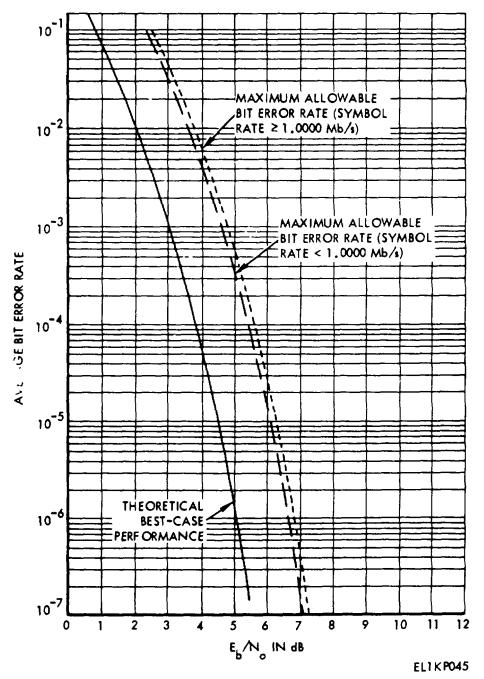

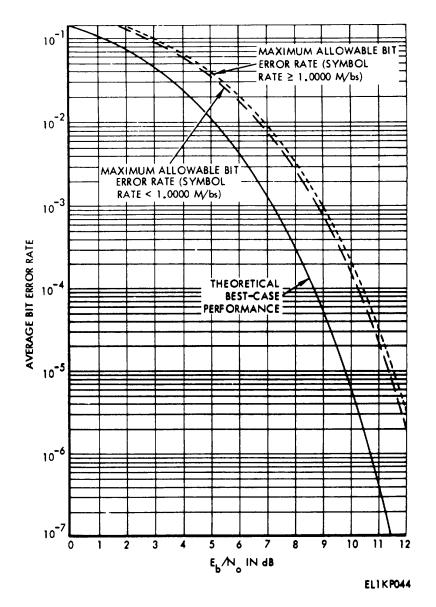

| 3-16                                   | Modem theoretical performance curves                                                                                                                                         |

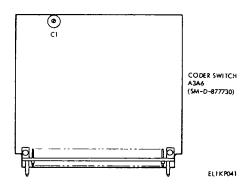

| 3-17                                   | Encoder switch test points and adjustment locations                                                                                                                          |

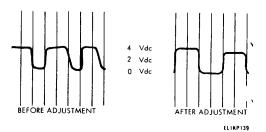

| 3-17.1                                 | Encoder switch timing alinement, dc clock waveforms                                                                                                                          |

| 3-18                                   | Phase and loss of lock detector, adjustment locations                                                                                                                        |

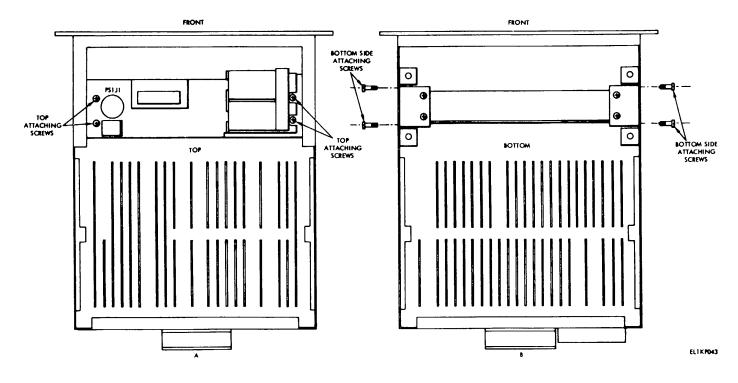

| 3-19                                   | Power supply removal and replacement                                                                                                                                         |

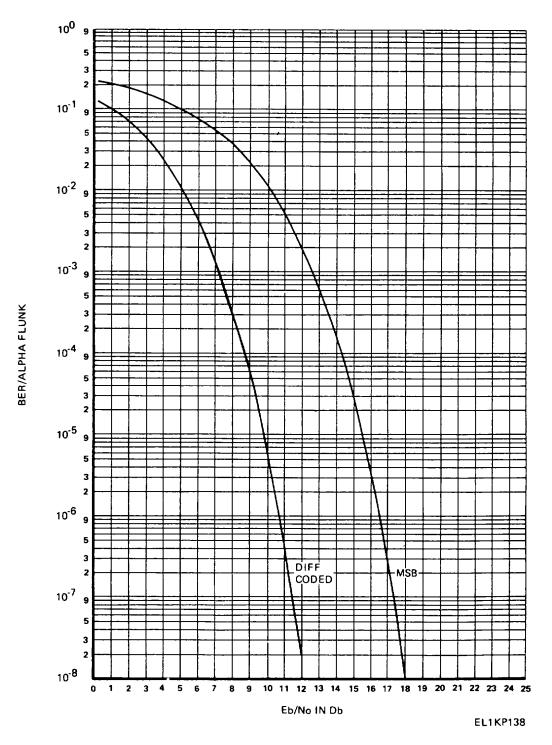

| 3-20                                   | QPSK/BPSK modem bit error rate performance for differential coding and no error-correcting coding                                                                            |

| 3-21                                   | QPSK/BPSK modem error rate performance for differential coding and external (KY-801/GSC                                                                                      |

| ~ _ !                                  | (Viterbi) soft decision, $K = 7$ ) error-correcting coding                                                                                                                   |

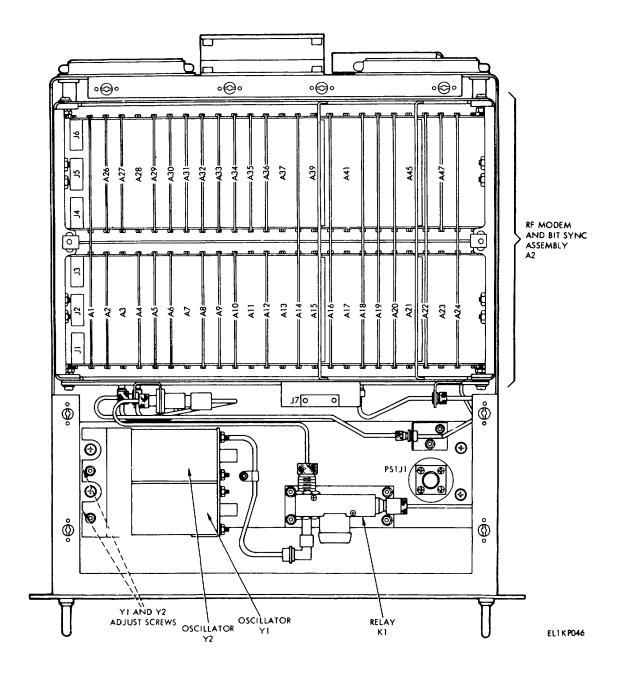

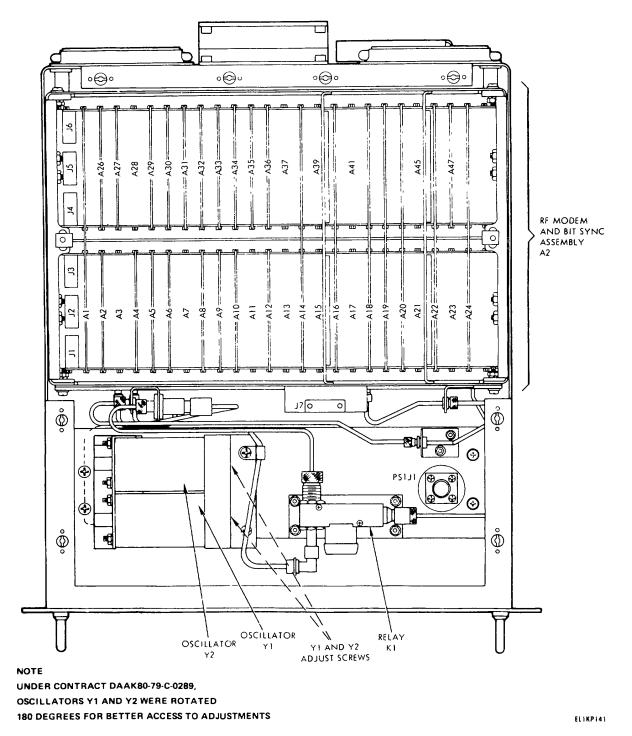

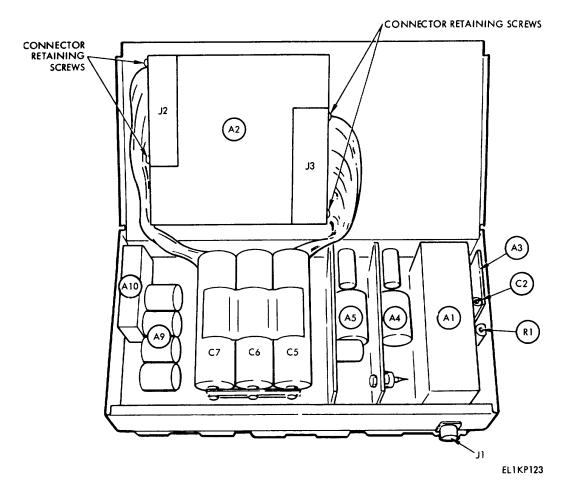

| 3-22                                   | QPSK/BPSK modem, top view (top cover removed)                                                                                                                                |

|                                        |                                                                                                                                                                              |

| 3-22.1                                 | QPSK/BPSK modem (Y 1 and Y2 rotated) top view, top cover removed                                                                                                             |

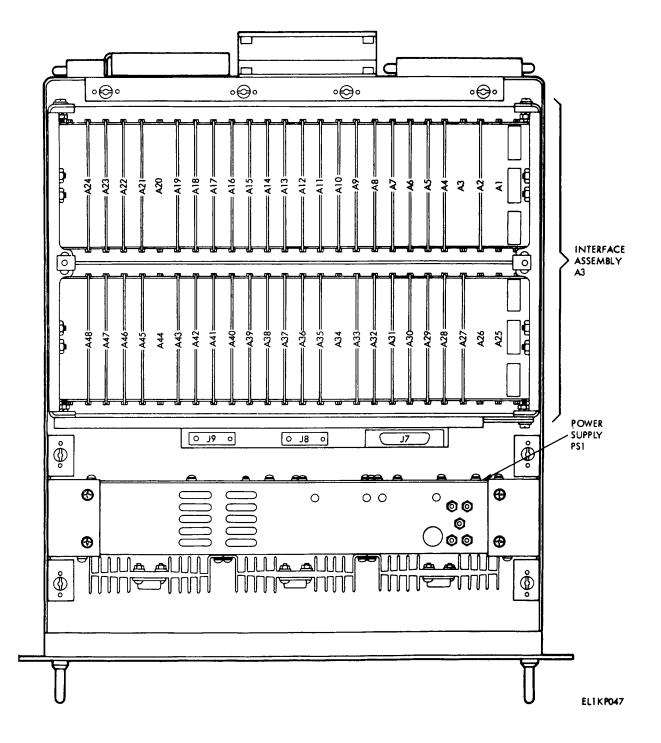

| 3-23                                   | QPSK/BPSK modem, bottom view (bottom cover removed)                                                                                                                          |

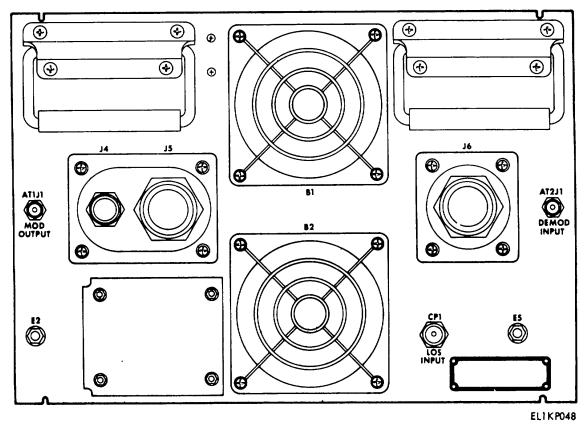

| 3-24                                   | QPSK/BPSK modem, rear view                                                                                                                                                   |

| 3-25                                   | Data detector and driver, test points and adjustment locations                                                                                                               |

| 3-26                                   | 70 MHz input range selection switch S1, 70 MHz gain control amplifier card, A2A16                                                                                            |

| 5-1                                    | Power supply PS1, external view                                                                                                                                              |

| 5-2                                    | Power supply, top view with top cover open                                                                                                                                   |

| -                                      | Dc power supply block diagram                                                                                                                                                |

| 5-3                                    | Example of dc-to-dc converter                                                                                                                                                |

| 5-3                                    |                                                                                                                                                                              |

| 5-3<br>5-4                             |                                                                                                                                                                              |

| 5-3<br>5-4<br>5-5                      | Regulator and output circuit block diagram                                                                                                                                   |

| 5-3<br>5-4<br>5-5<br>5-6               | Regulator and output circuit block diagram<br>+ 15 volt voltage regulator                                                                                                    |

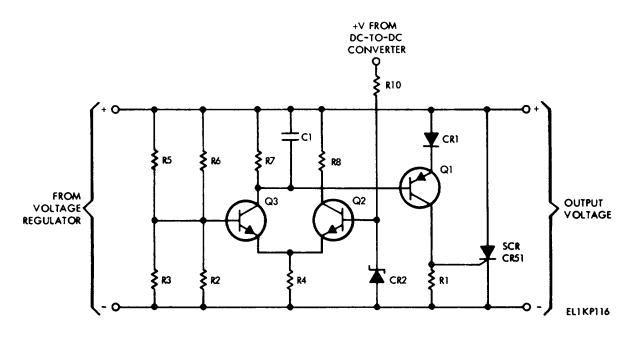

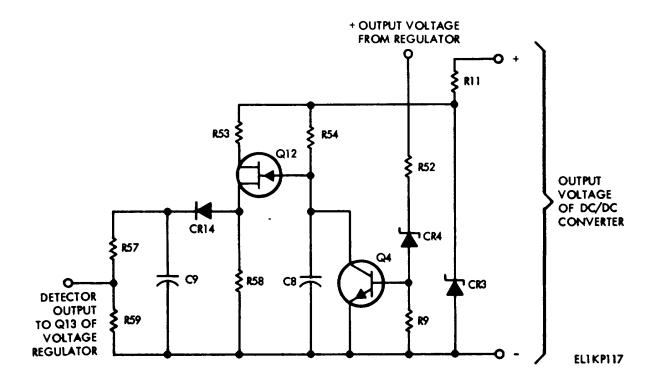

| 5-3<br>5-4<br>5-5<br>5-6<br>5-7        | Regulator and output circuit block diagram<br>+ 15 volt voltage regulator<br>Overvoltage protector, simplifier schematic diagram                                             |

| 5-3<br>5-4<br>5-5<br>5-6<br>5-7<br>5-8 | Regulator and output circuit block diagram<br>+ 15 volt voltage regulator<br>Overvoltage protector, simplifier schematic diagram<br>Example of undervoltage detector circuit |

| 5-3<br>5-4<br>5-5<br>5-6<br>5-7        | Regulator and output circuit block diagram<br>+ 15 volt voltage regulator<br>Overvoltage protector, simplifier schematic diagram                                             |

Change2 iii

|                       | TM 11-5820-847-34/NAVELEX 0969-LP-169-502                                                                                                             | 0/TO 31R5    |

|-----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|

| <i>Fig No</i><br>5-11 | <i>Title</i> Typical dc output showing ripple characteristics                                                                                         | 5-11         |

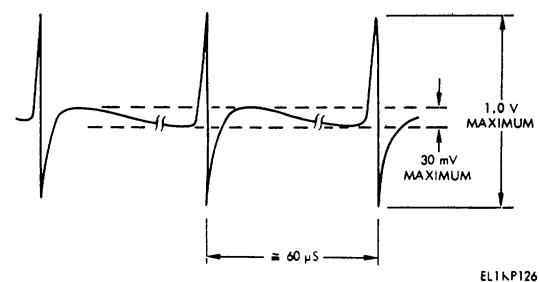

| 5-11<br>5-12          | Dc-to-dc converter-typical waveforms                                                                                                                  | 5-11<br>5-22 |

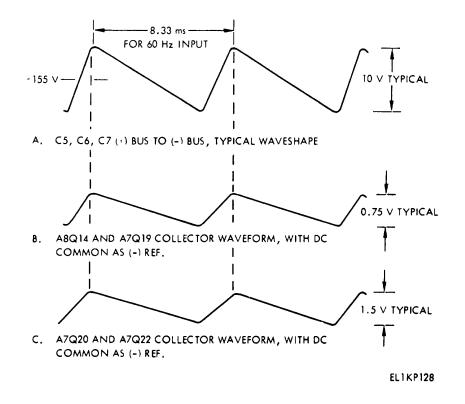

| 5-12                  | Typical input filter and output drive circuit waveforms                                                                                               | 5-23         |

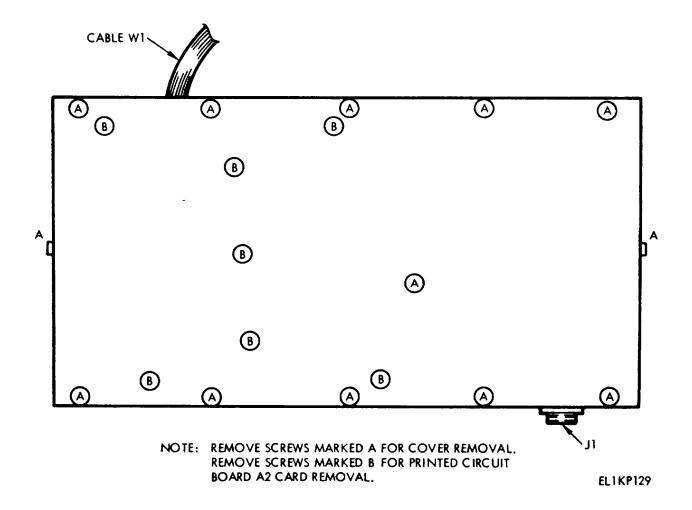

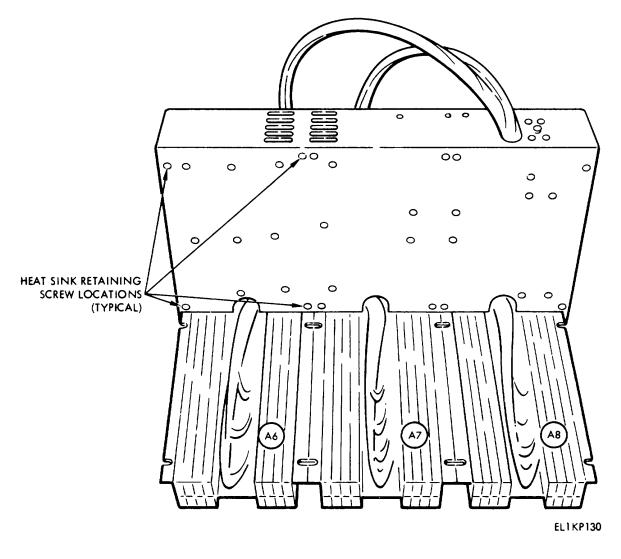

| 5-14                  | Top view of power supply                                                                                                                              | 5-24         |

| 5-15                  | Bottom of power supply chassis with heat sinks folded out                                                                                             | 5-25         |

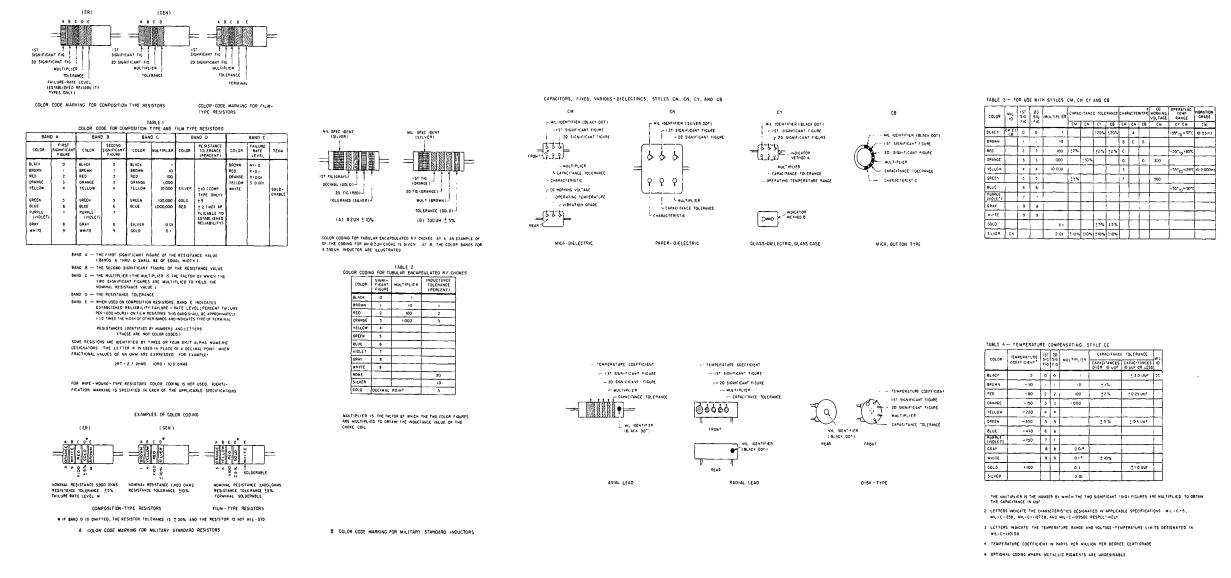

| FO-1                  | Color code markings for MIL-STD resistors, inductors, and capacitors                                                                                  | Located in   |

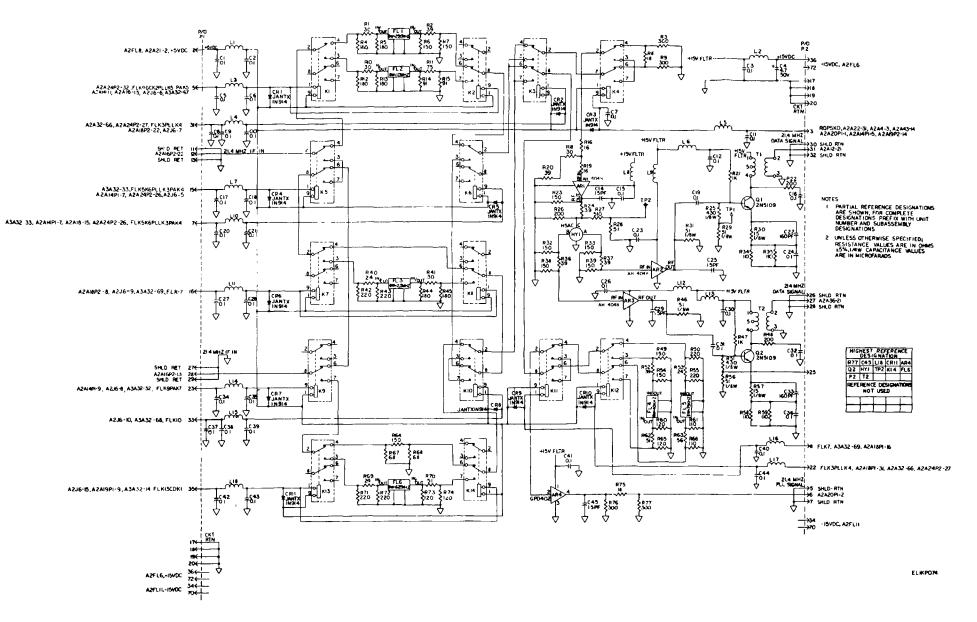

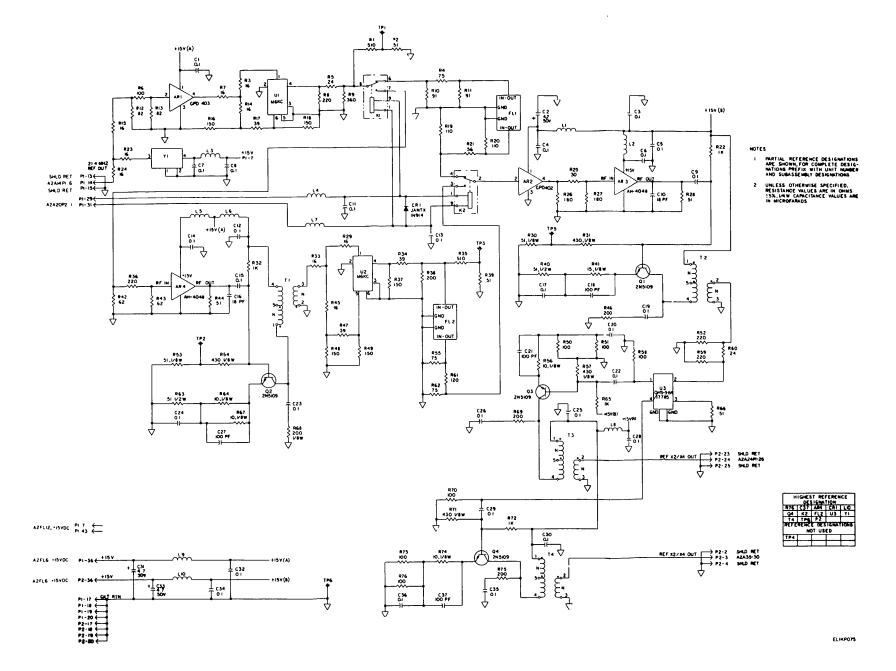

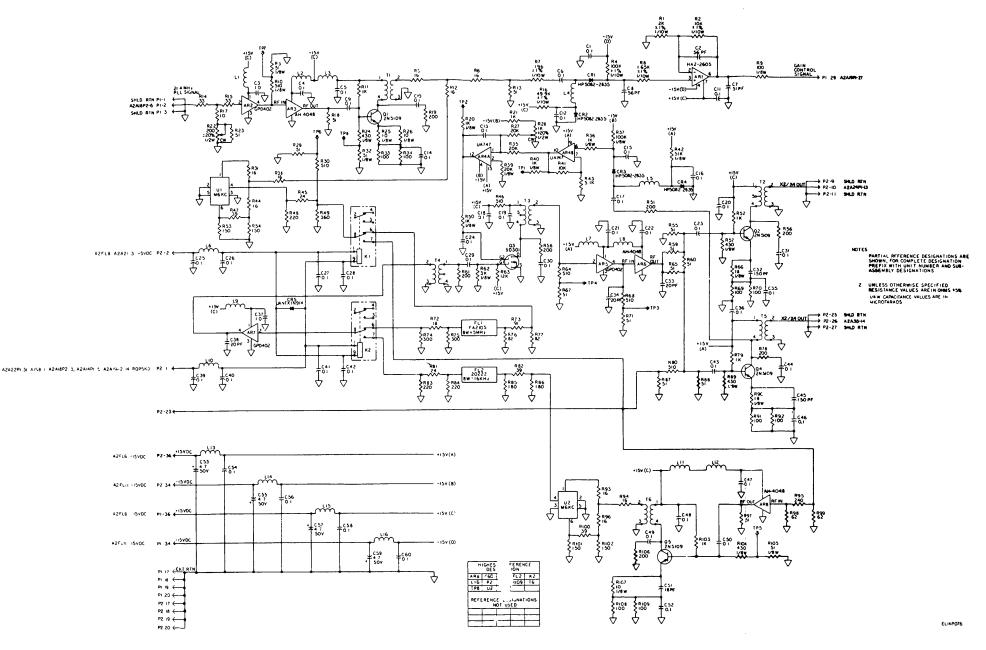

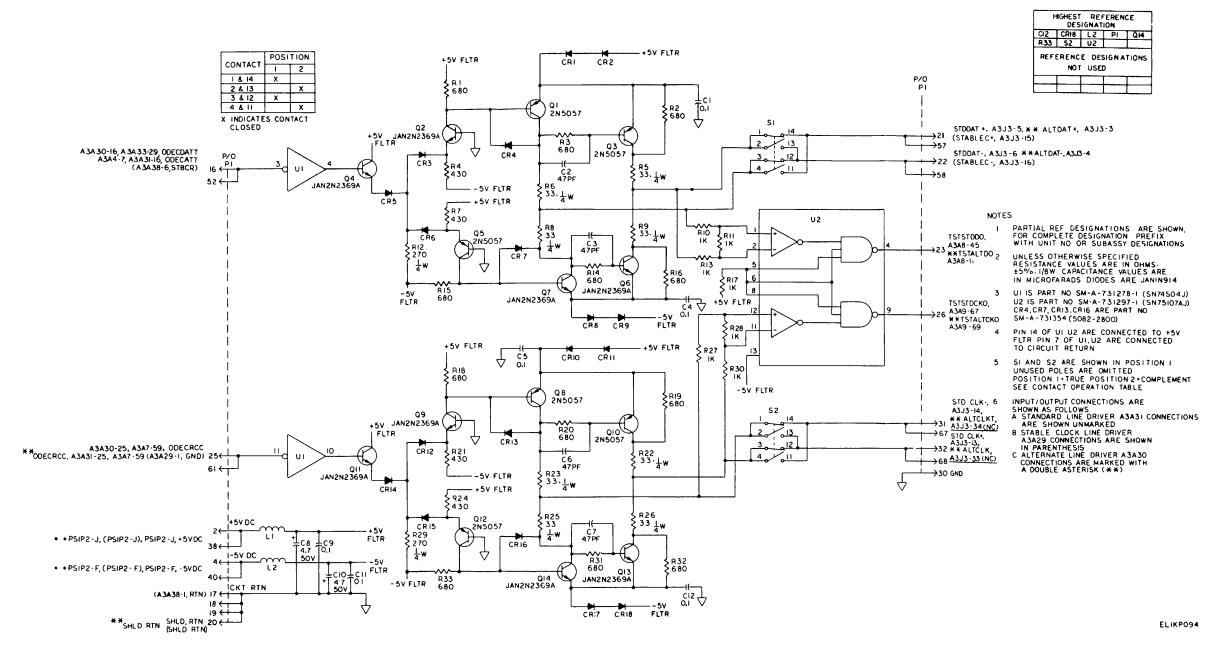

| FO-2                  | LOS/cable receiver and decoder, A3A2 (SM-D-742089) schematic diagram                                                                                  | Back of      |

| FO-3                  | Input interface, A3A5 (SM-D-742037), schematic diagram                                                                                                | Manual       |

| FO-4                  | Transmit bit detector, A3A35 (SM-0-742045) schematic diagram                                                                                          |              |

| FO-5                  | Loop filter, A3A14 and A3A36 (SM-D-731221), schematic diagram                                                                                         |              |

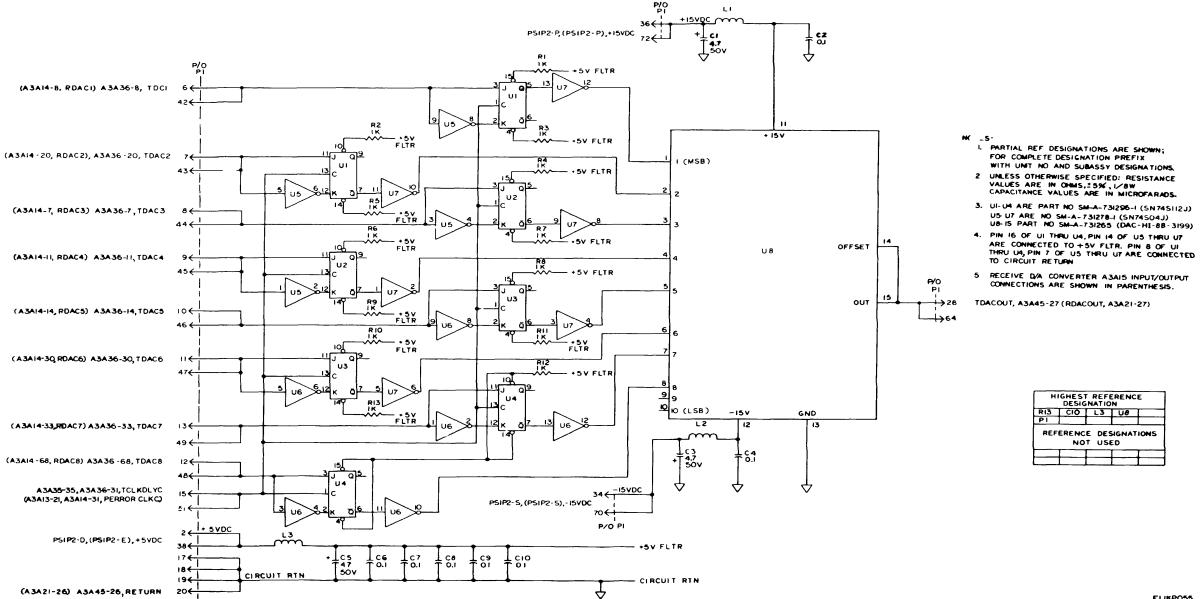

| FO-6                  | Digital-to-analog converter, A3A15 and A3A37 (SM-D-731217), schematic diagram                                                                         |              |

| FO-7<br>FO-8          | Reference oscillator, A3A19 and A3A43 (SM-D-742129), schematic diagram<br>Reference divider, A3A18, A3A38, and A3A42 (SM-D-742133), schematic diagram |              |

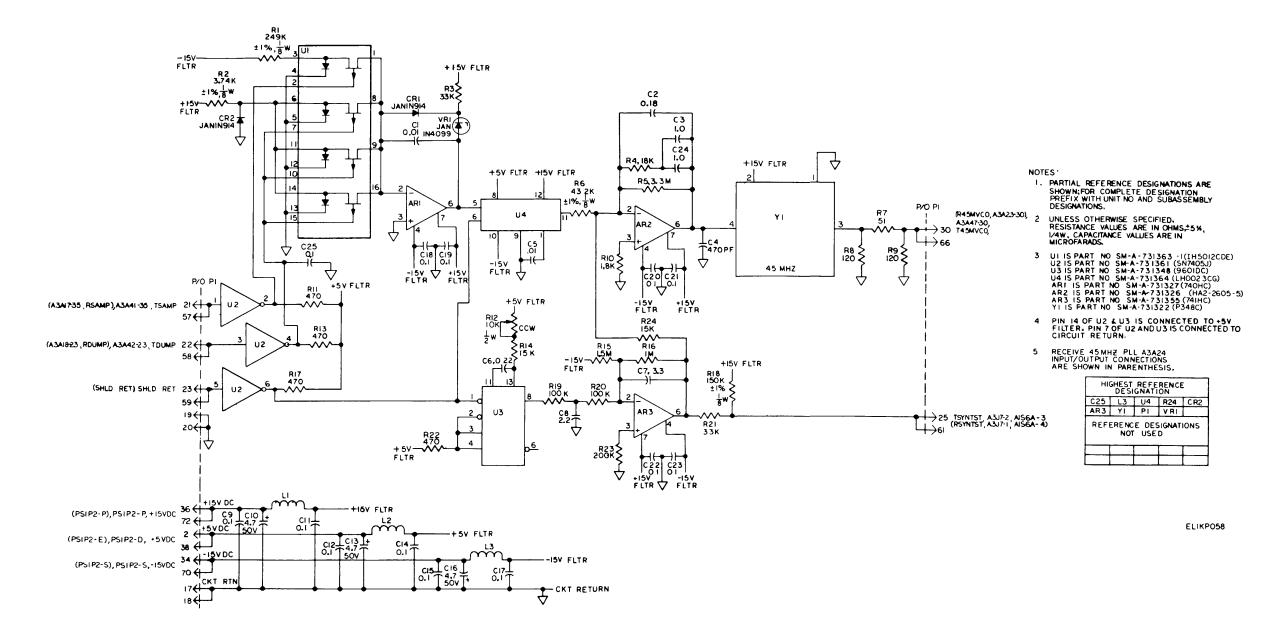

| FO-8<br>FO-9          | 45-MHz phase lock loop, A3A24 and A3A48 (SM-D-742113), schematic diagram                                                                              |              |

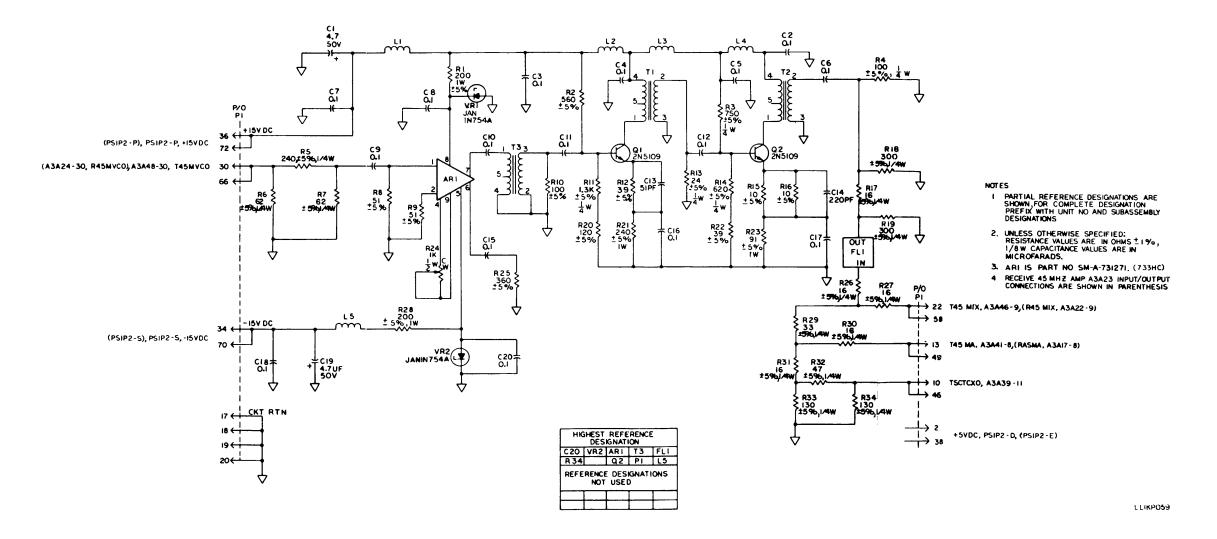

| FO-10                 | 45-MHz amplifier A3A23 and A3A47 (SM-D-742117), schematic diagram.                                                                                    |              |

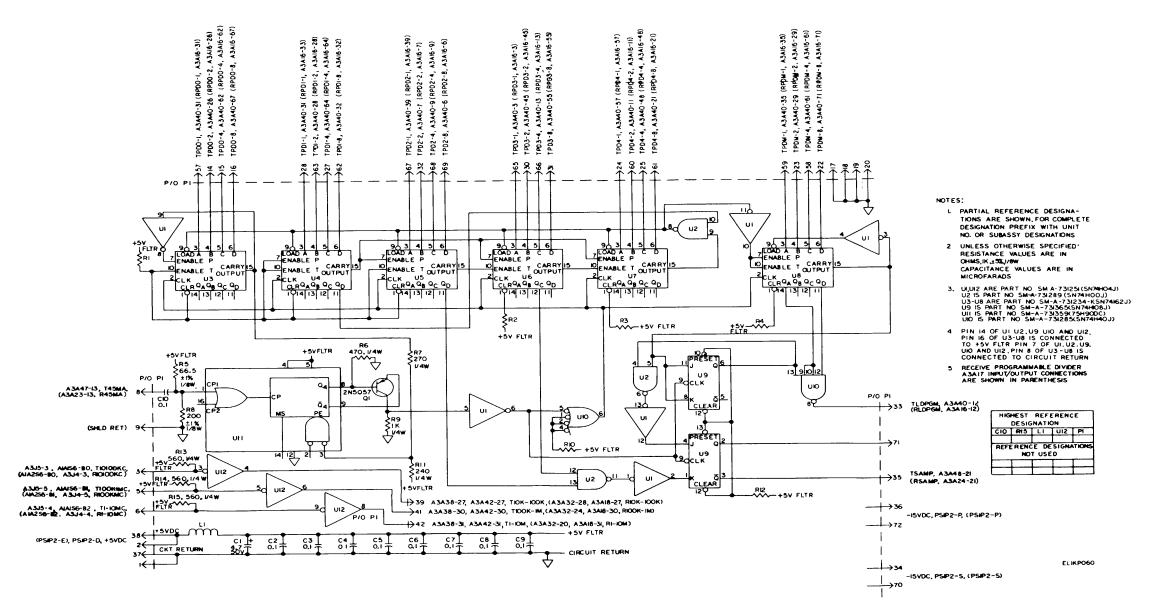

| FO-11                 | Programmable divider, A3A17 and A3A41 (SM-D-742109), schematic diagram.                                                                               |              |

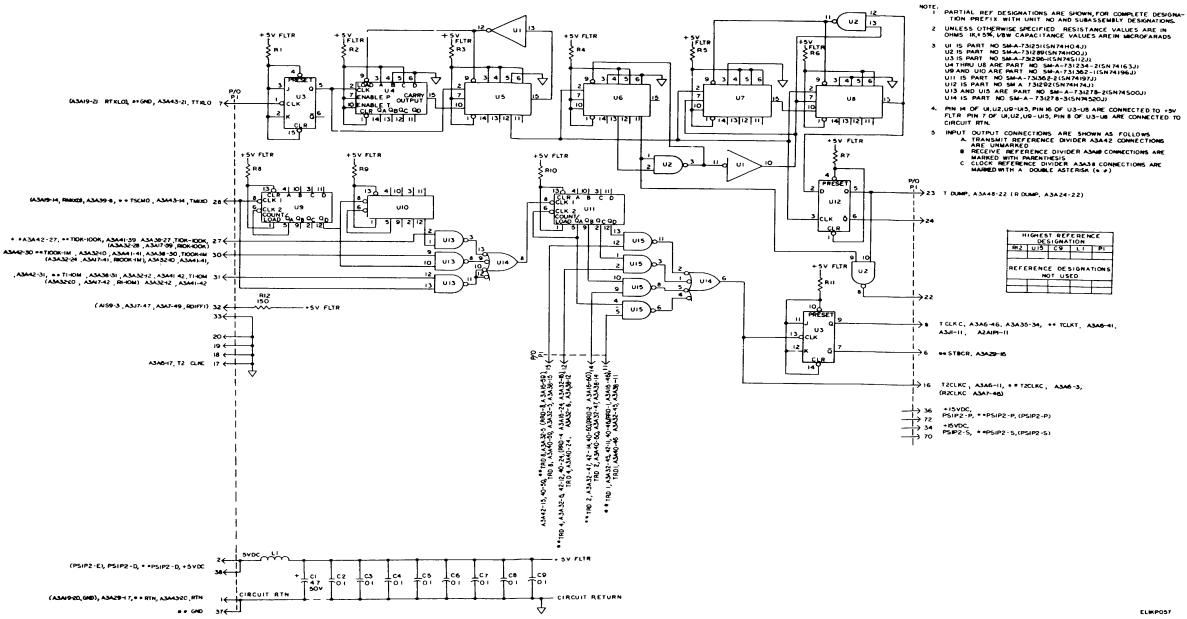

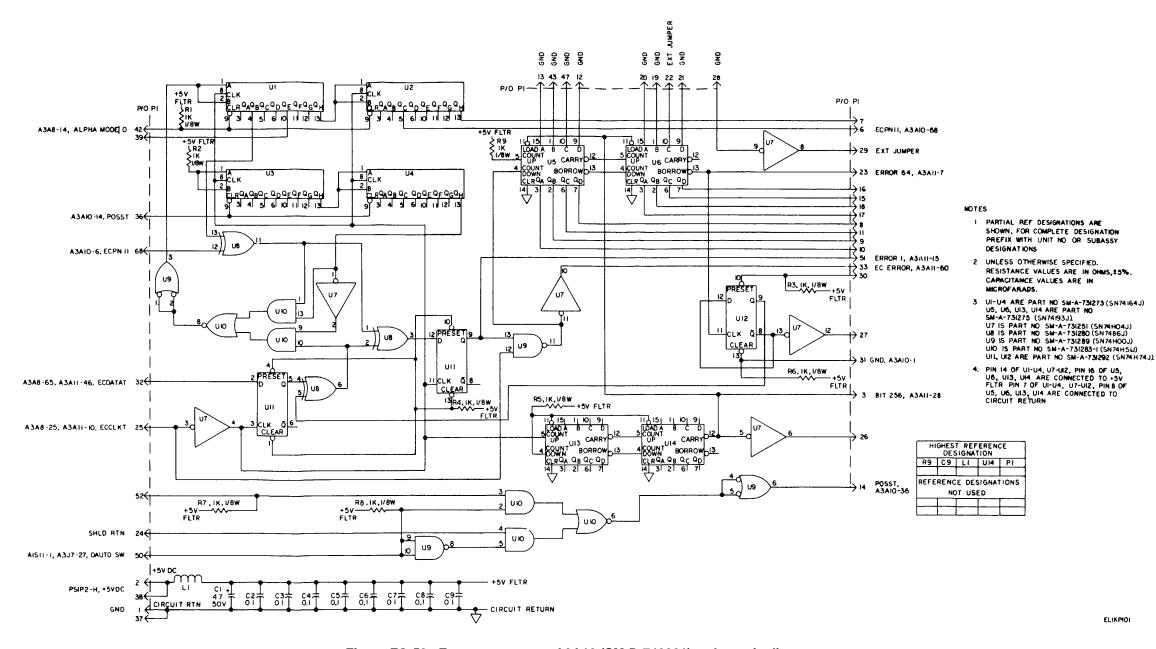

| FO-12                 | Counter encoder A3A16 and A3A40 (SM-D-742105), schematic diagram                                                                                      |              |

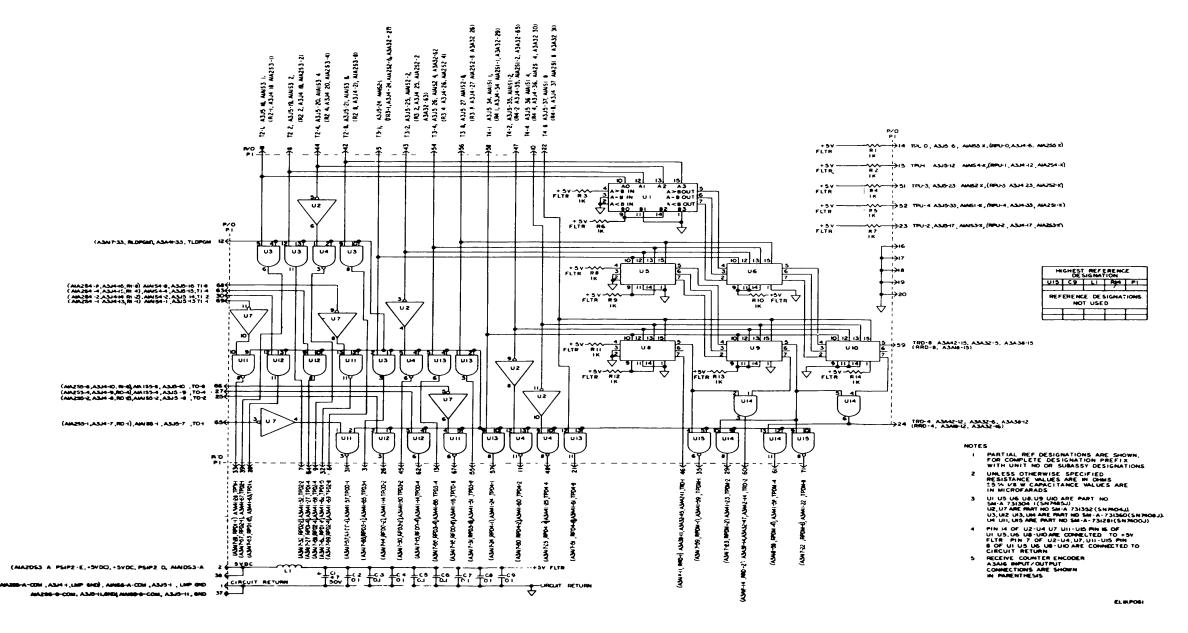

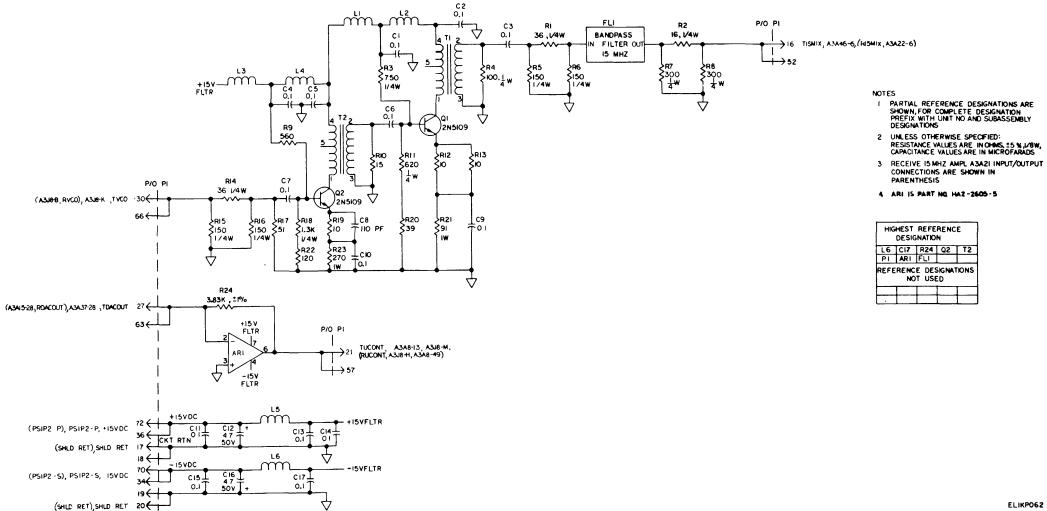

| FO-13                 | 15-MHz amplifier, A3A21 and A3A45 (SM-D-742121), schematic diagram                                                                                    |              |

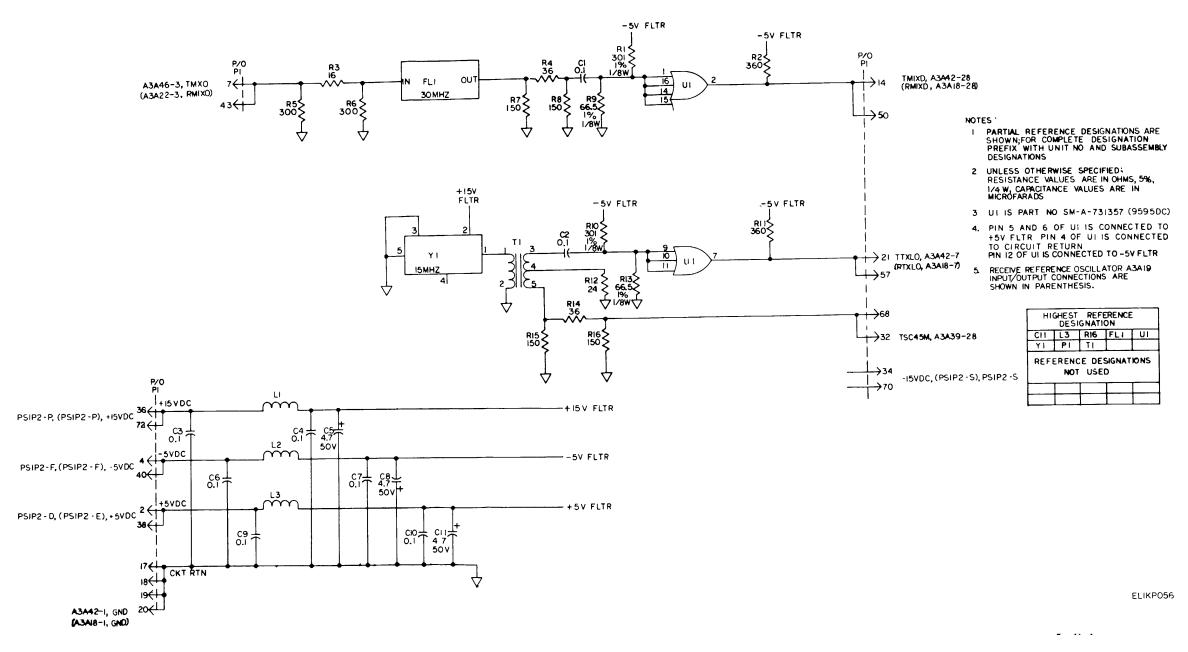

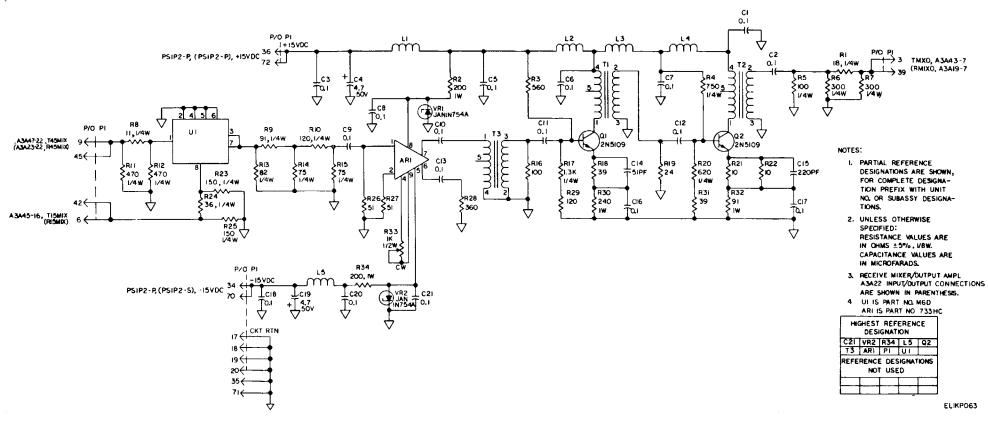

| FO-14                 | Mixer/output amplifier, A3A22 and A3A46 (SM-D-742125), schematic diagram                                                                              |              |

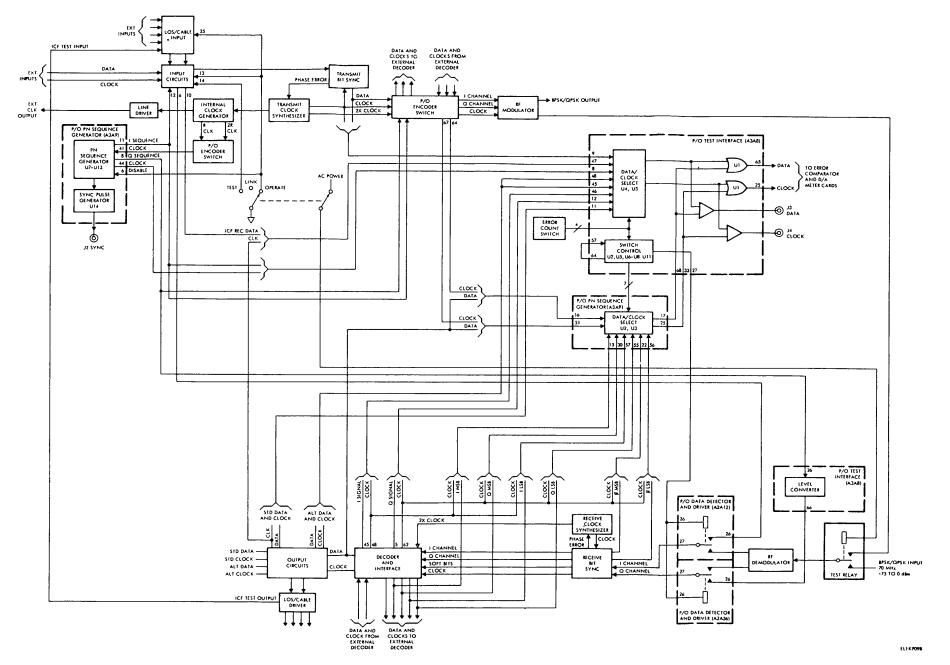

| FO-15                 | Encoder and interface, functional block diagram                                                                                                       |              |

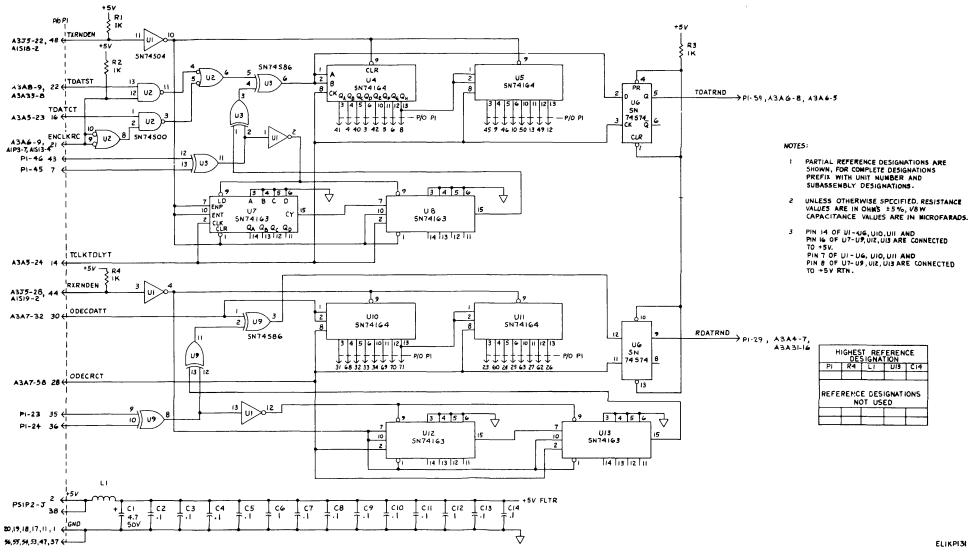

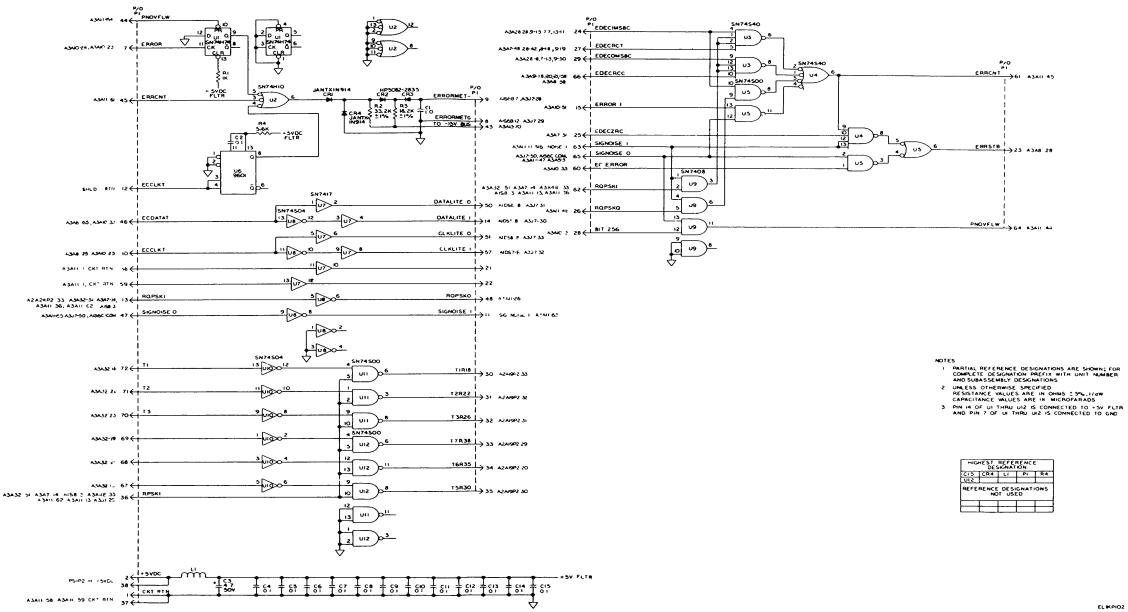

| FO-16                 | Randomizer/derandomizer, A3A33 (SM-D-877780), schematic diagram                                                                                       |              |

| FO-17                 | Encode switch, A3A6 (SM-D-877730), schematic diagram                                                                                                  |              |

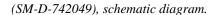

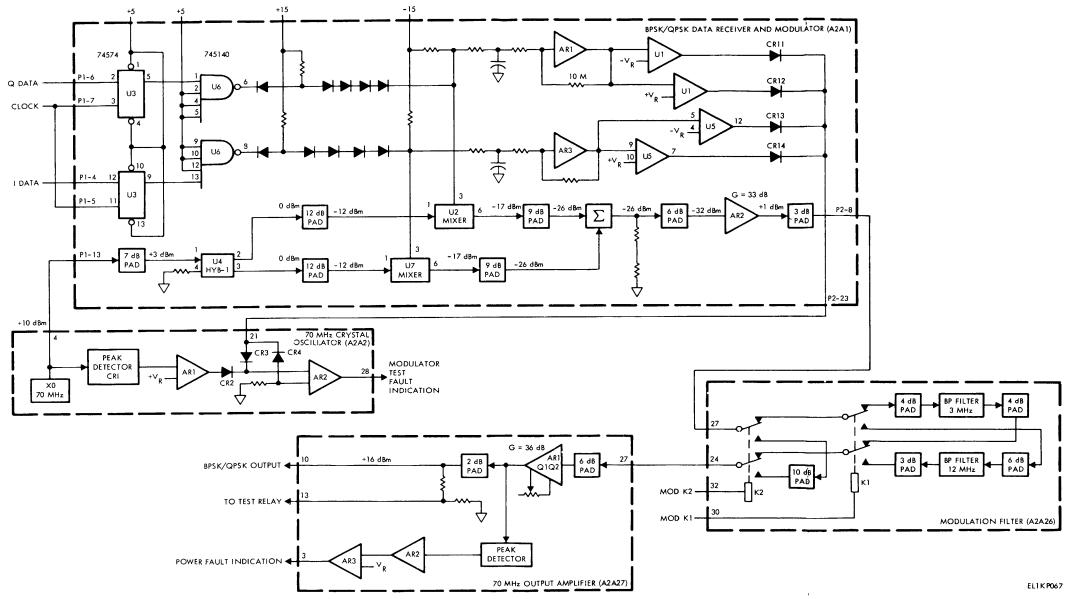

| FO-18                 | Encoder interface, A3A27 and A3A28 (SM-D-742049) schematic diagram                                                                                    |              |

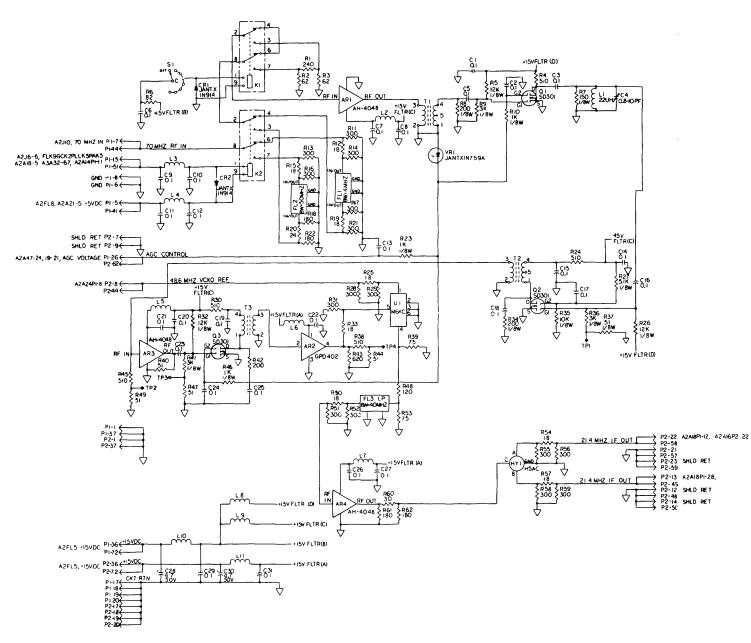

| FO-19<br>FO-20        | RF modulator, functional block diagram                                                                                                                |              |

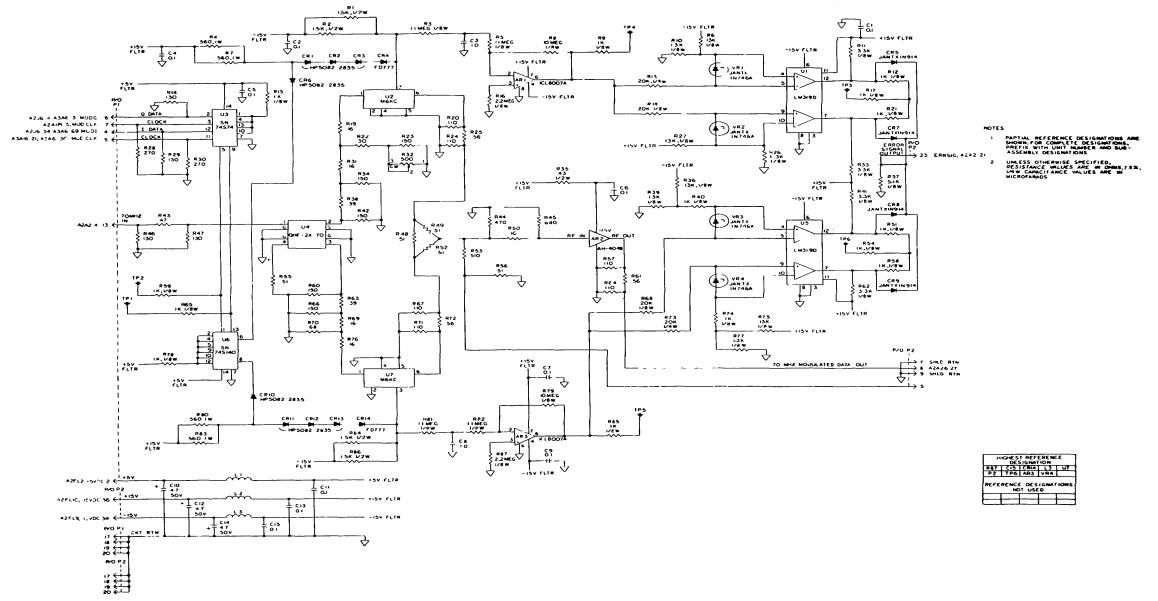

| FO-20<br>FO-21        | QPSK/BPSK data receiver and modulator, A2A1 (SM-D-877650), schematic diagram<br>70-MHz crystal oscillator, A2A2 (SM-D-731193) schematic diagram       |              |

| FO-21<br>FO-22        | Modulation filter, A2A26 (SM-D-731185), schematic diagram                                                                                             |              |

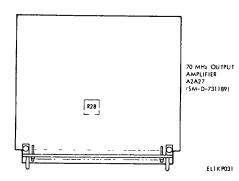

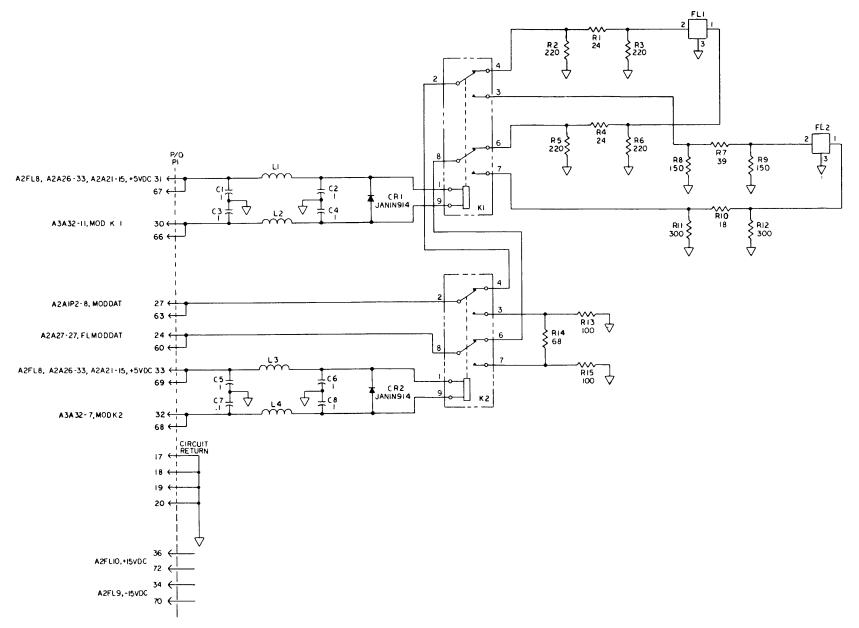

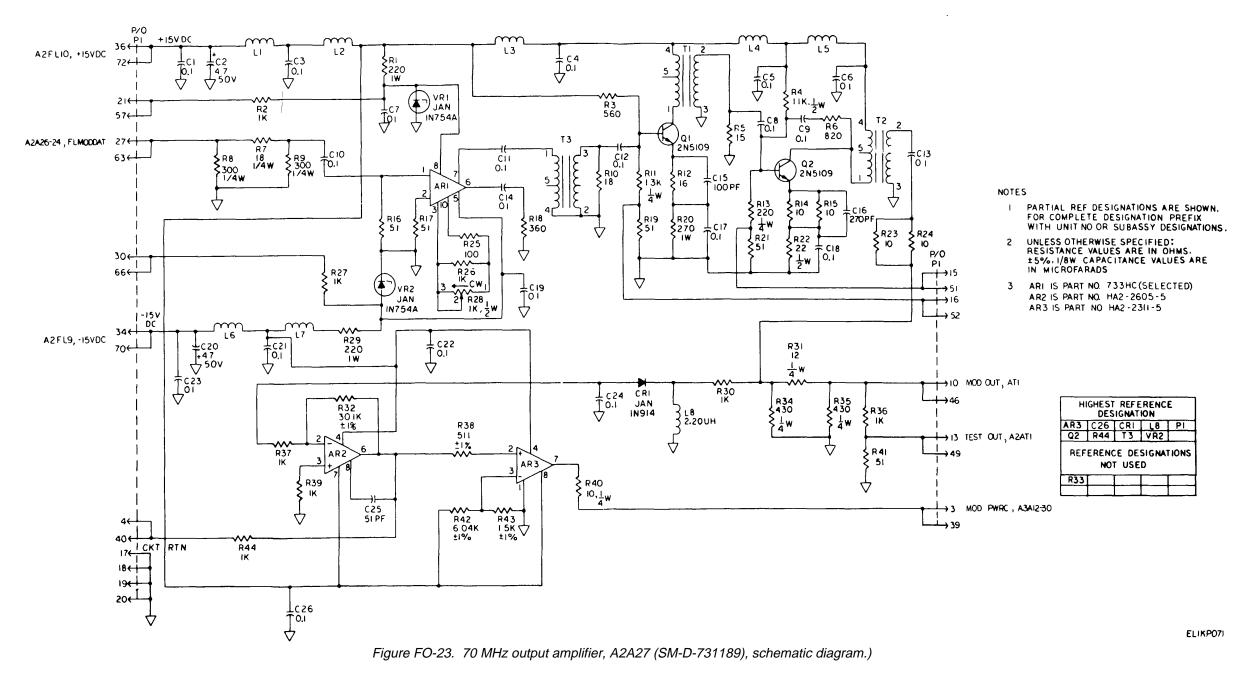

| FO-28                 | 70 MHz output amplifier, A2A27 (SM-D-731189), schematic diagram                                                                                       |              |

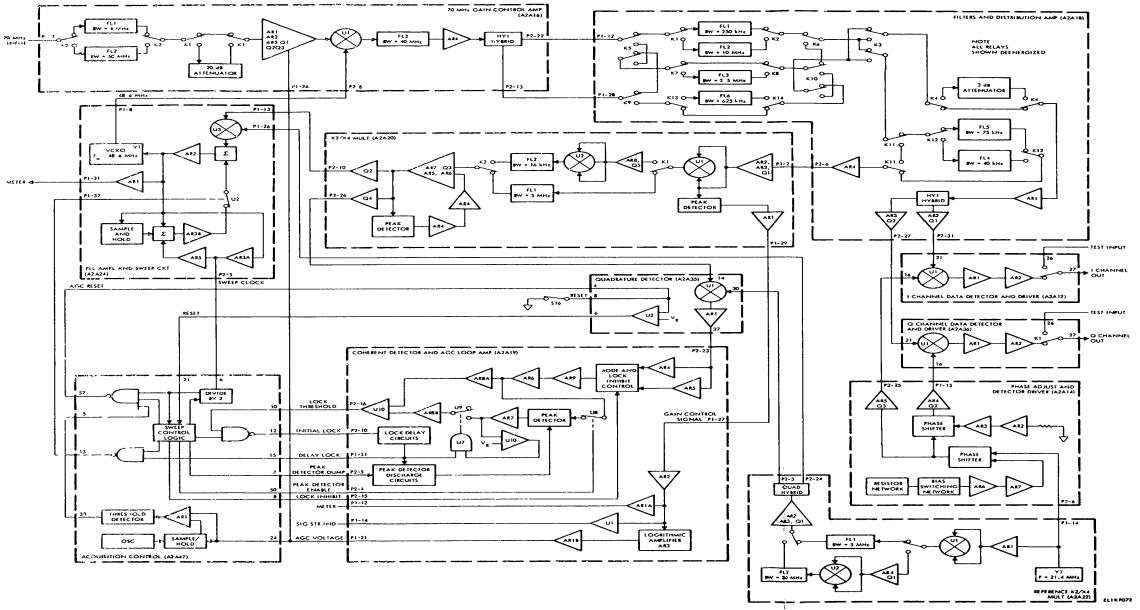

| FO-24                 | RF demodulator, functional block diagram                                                                                                              |              |

| FO-25                 | 70 MHz gain control amplifier, A2A16 (SM-D-877675), schematic diagram                                                                                 |              |

| FO-26                 | Filters and distribution amplifier, A2A18 (SM-D-877645), schematic diagram                                                                            |              |

| FO-27                 | Reference X2/X4 multiplier, A2A22 (SM-D-877655), schematic diagram                                                                                    |              |

| FO-28                 | X2/X4 multiplier, A2A20 (SM-D-877660), schematic diagram                                                                                              |              |

| FO-29                 | Quadrature detector, A2A35 (SM-D-877690), schematic diagram                                                                                           |              |

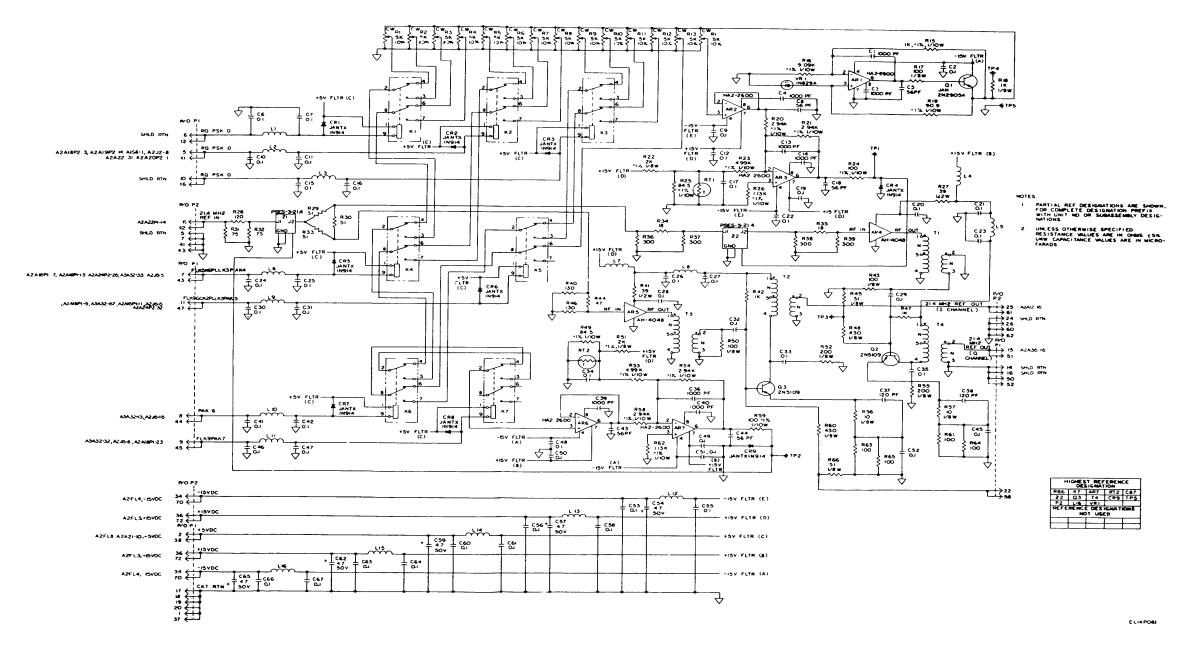

| FO-30                 | Coherent detector and AGC loop amplifier, A2A19 (SM-D-877665), schematic diagram                                                                      |              |

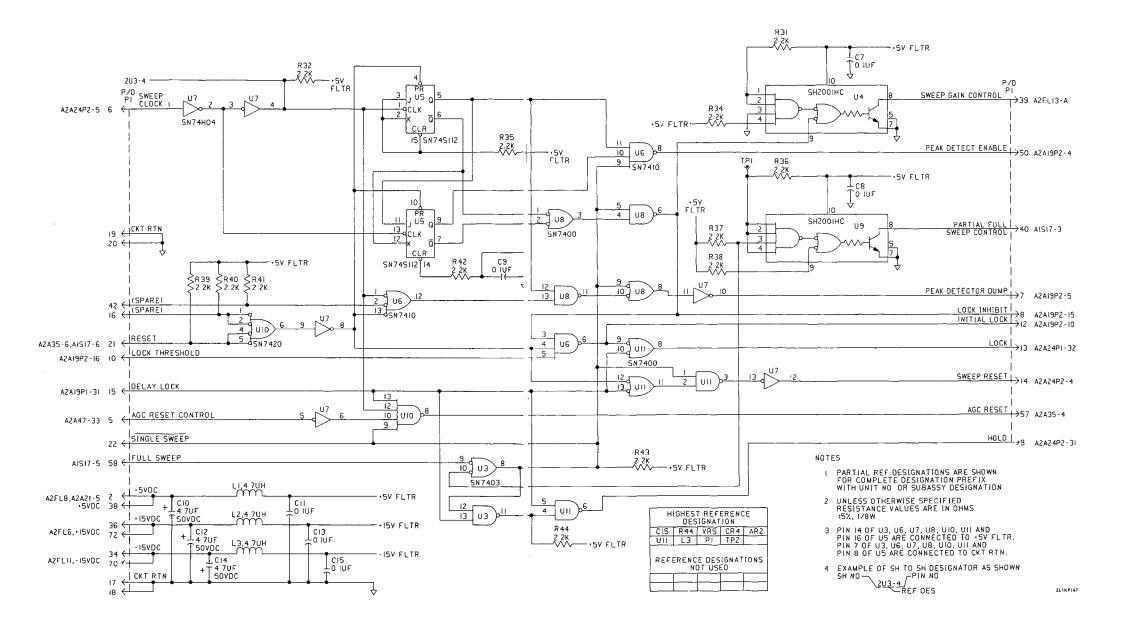

| FO-31<br>FO-32        | PLL amplifier and sweep generator, A2A24 (SM-D-877670), schematic diagram                                                                             |              |

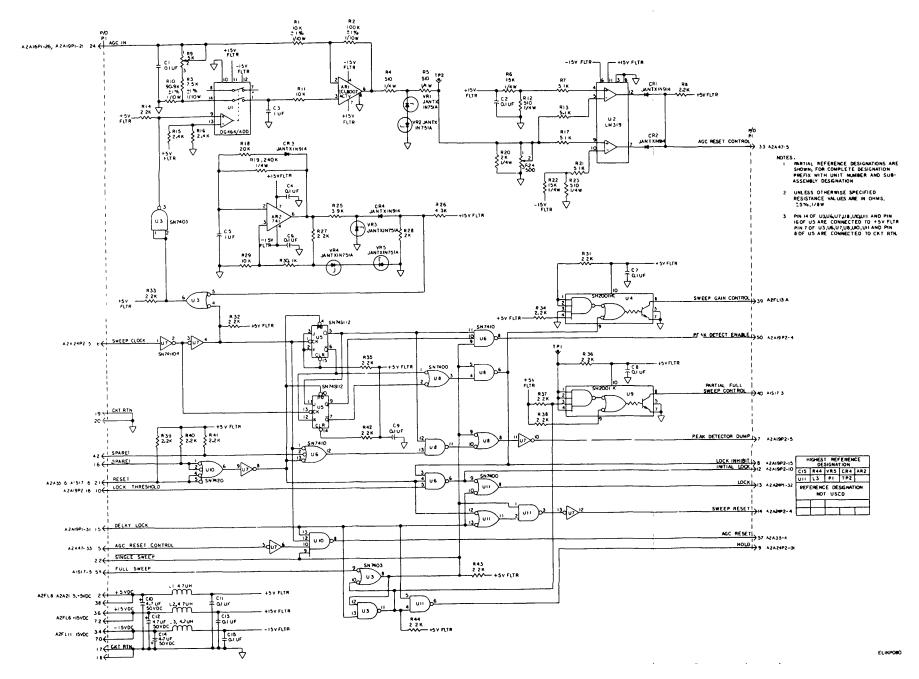

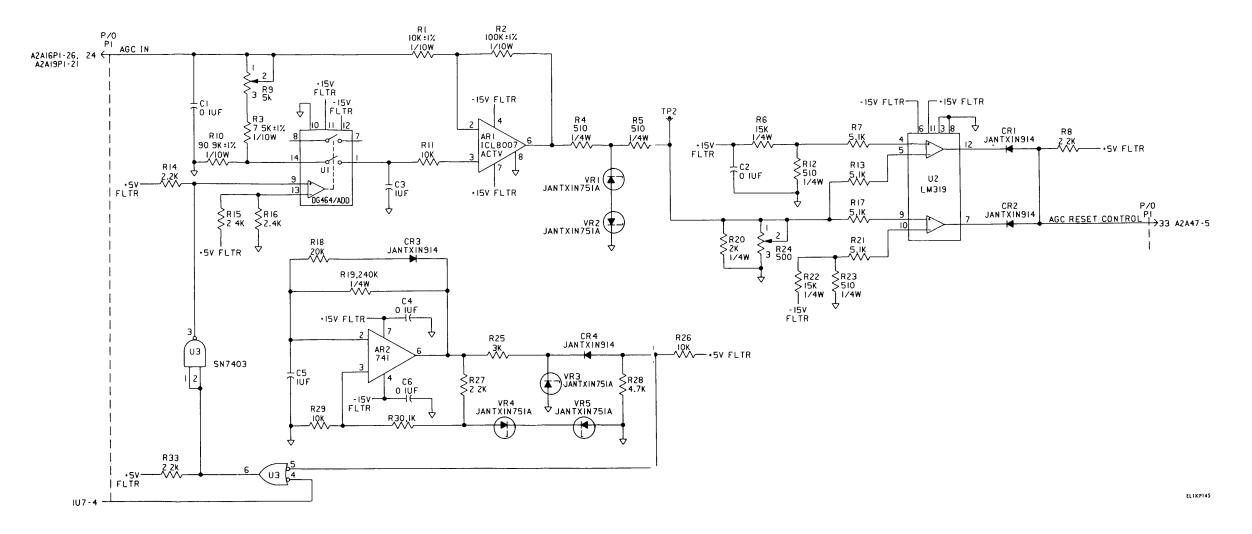

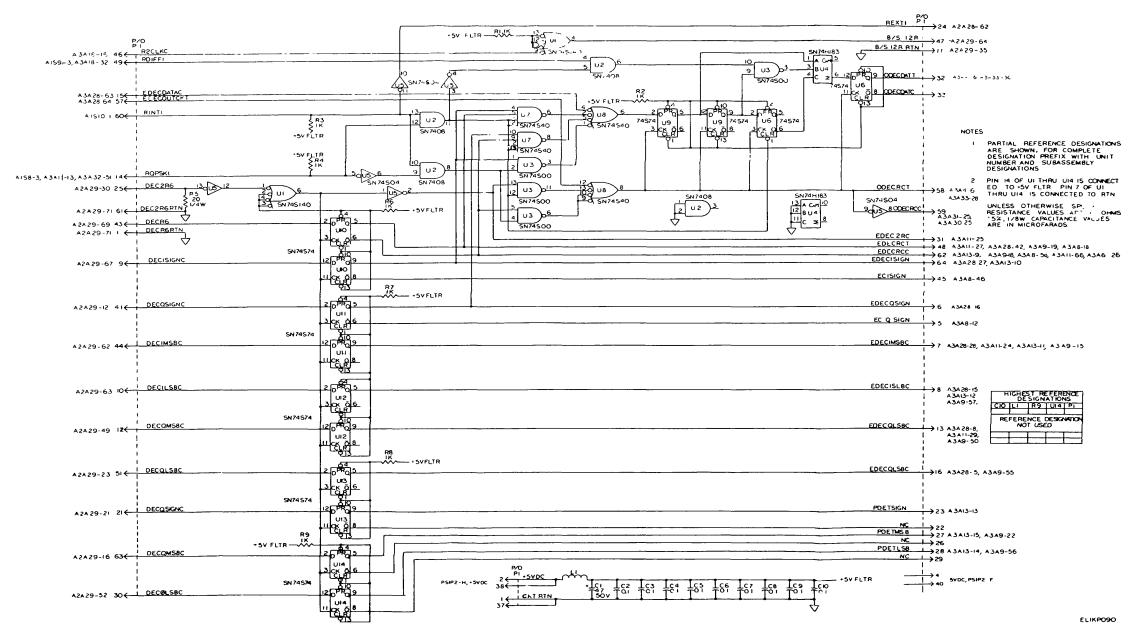

| FO-32<br>FO-32.1      | Acquisition control, A2A47 (SM-D-877685), schematic diagram<br>Acquisition control, A2A47 (SM-D-877935), schematic diagram (2 sheets)                 |              |

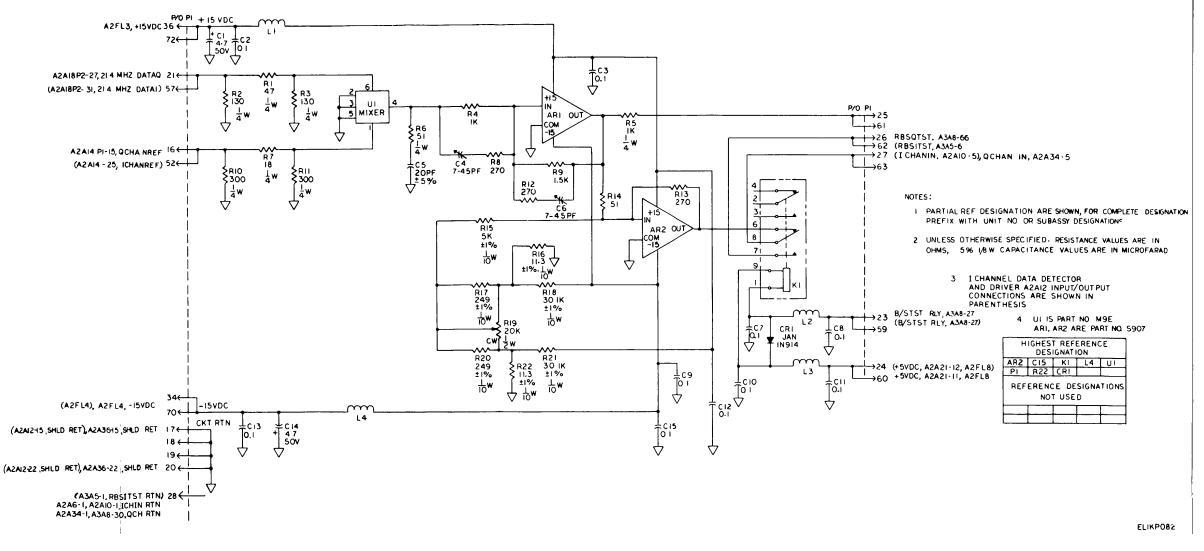

| FO-32.1               | Phase adjust and detector drive, A2A14 (SM-D-877680), schematic diagram                                                                               |              |

| FO-34                 | Data detector and driver A2A12 and A2A36 (SM-D-731178) schematic diagram                                                                              |              |

| FO-35                 | Relay control, A3A32 (SM-D-877710), schematic diagram                                                                                                 |              |

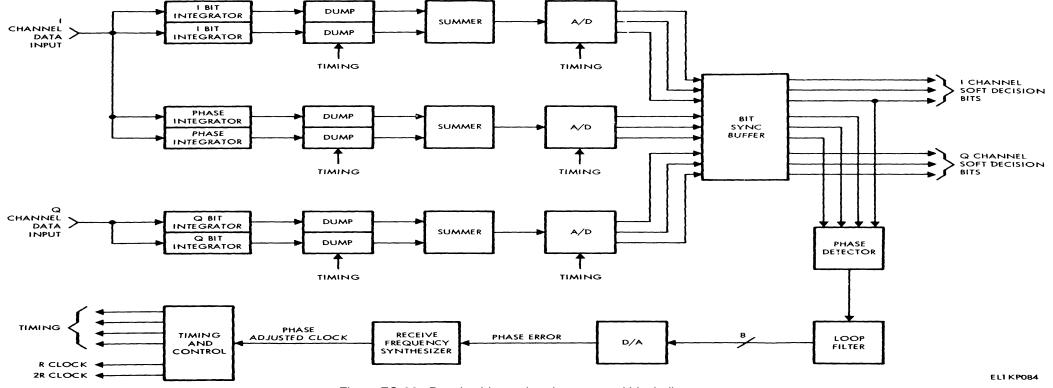

| FO-36                 | Receive bit synchronizer, general block diagram                                                                                                       |              |

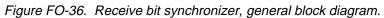

| FO-37                 | Receive bit synchronizer, functional block diagram                                                                                                    |              |

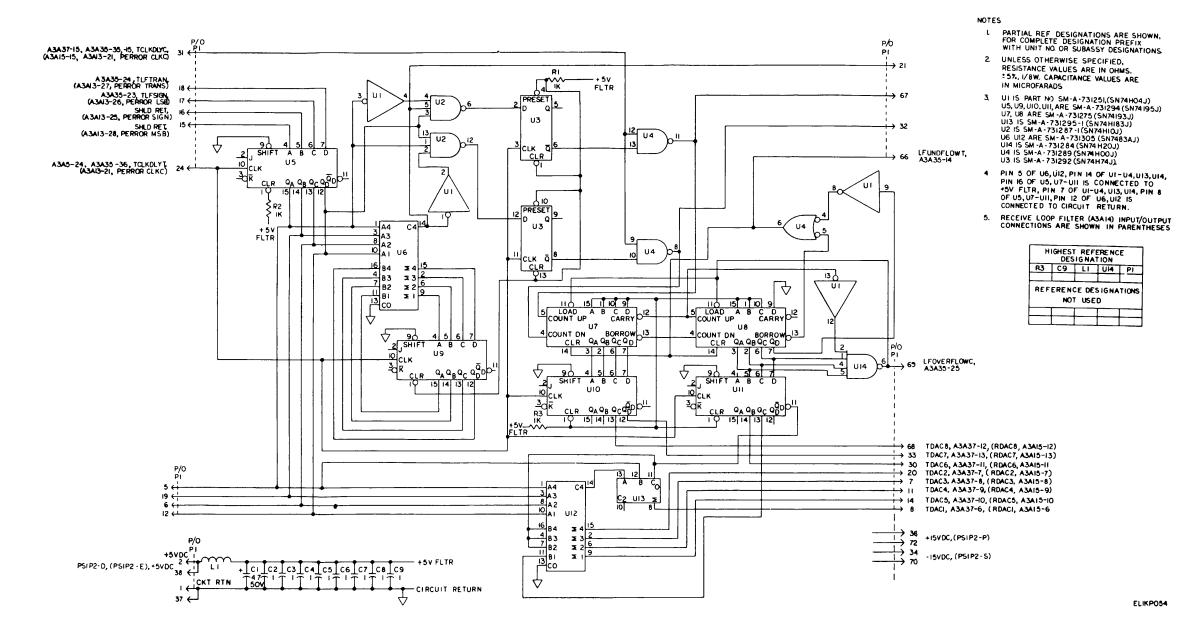

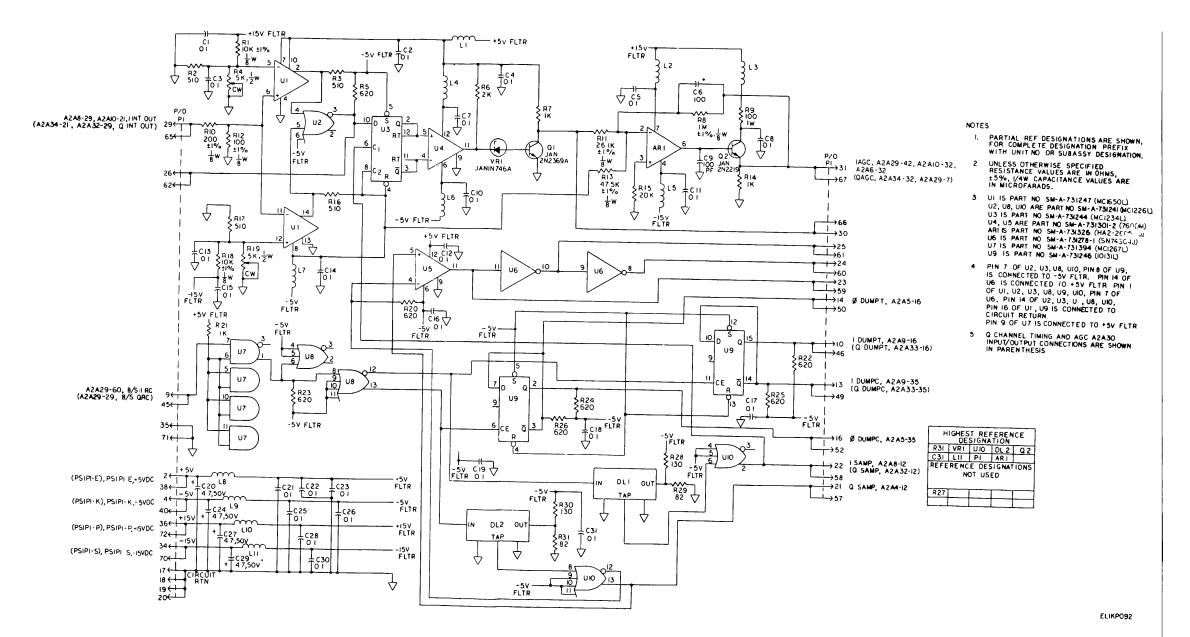

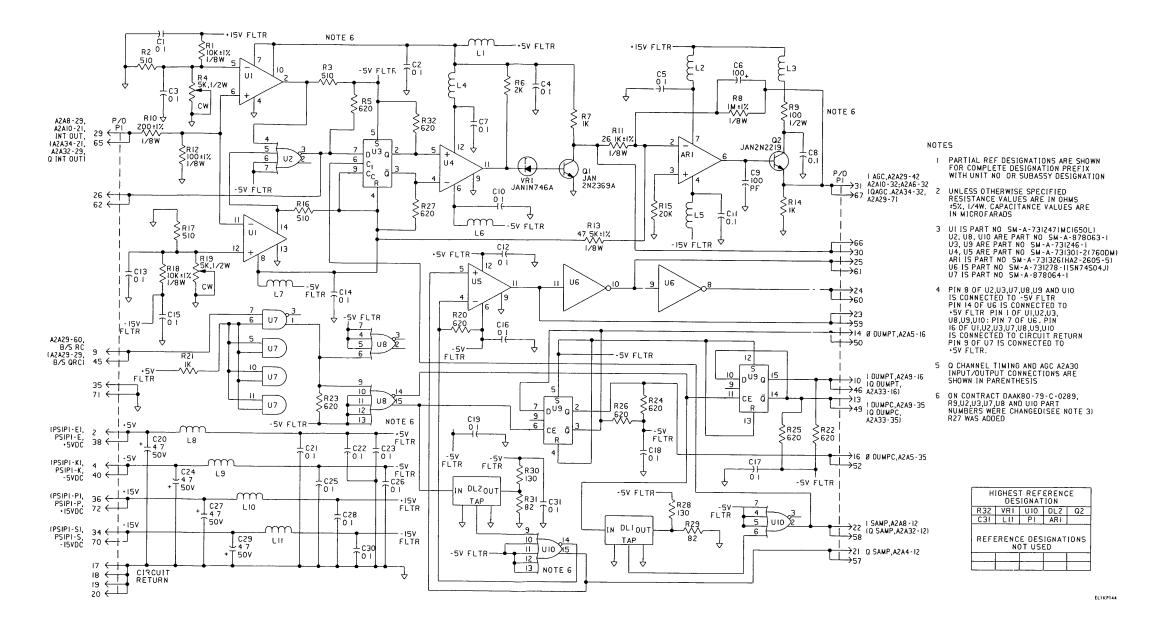

| FO-38                 | Integrator, A2A6, A2A10 and A2A34 (SM-D-731205), schematic diagram                                                                                    |              |

| FO-39                 | Dump circuit, A2A5, A2A9, and A2A33 (SM-D-731209), schematic diagram                                                                                  |              |

| FO-40                 | Quantizer, A2A4, A2A8, and A2A32 (SM-D-731213), schematic diagram                                                                                     |              |

| FO-41                 | Bit sync buffer, A2A29 (SM-D-877695), schematic diagram                                                                                               |              |

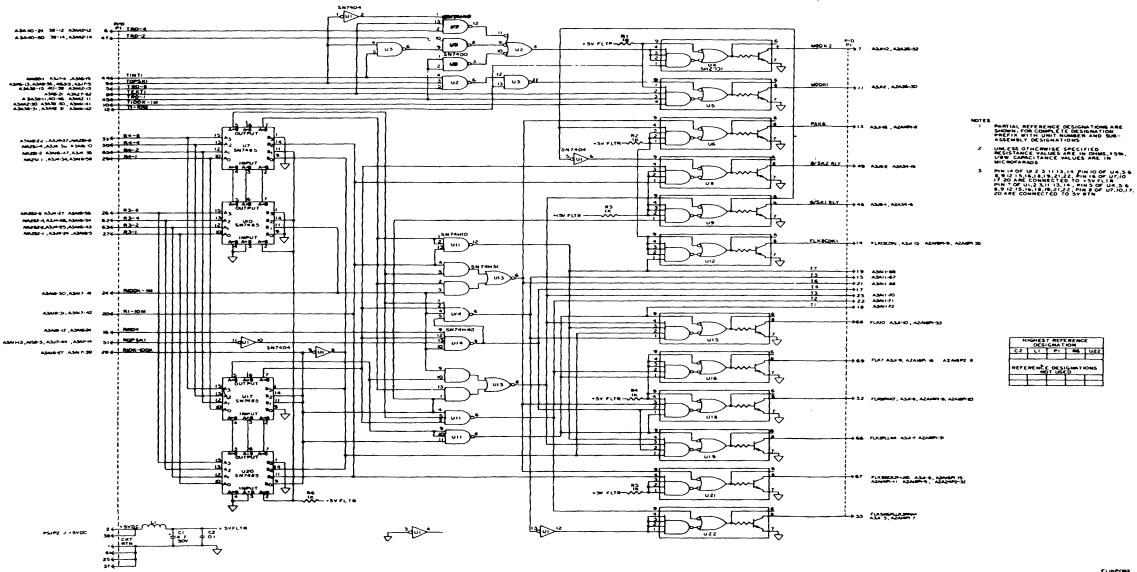

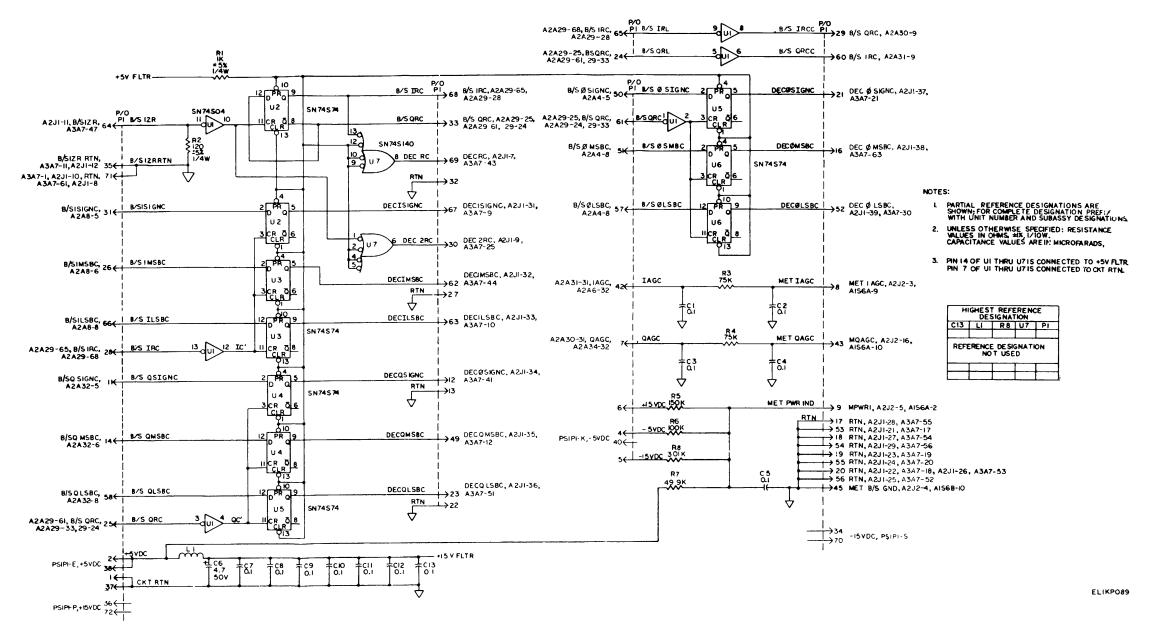

| FO-42                 | Decoder switch, A3A7 (SM-D-877700), schematic diagram                                                                                                 |              |

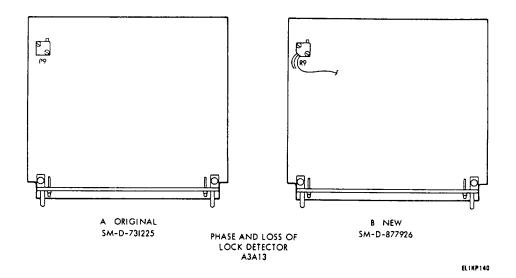

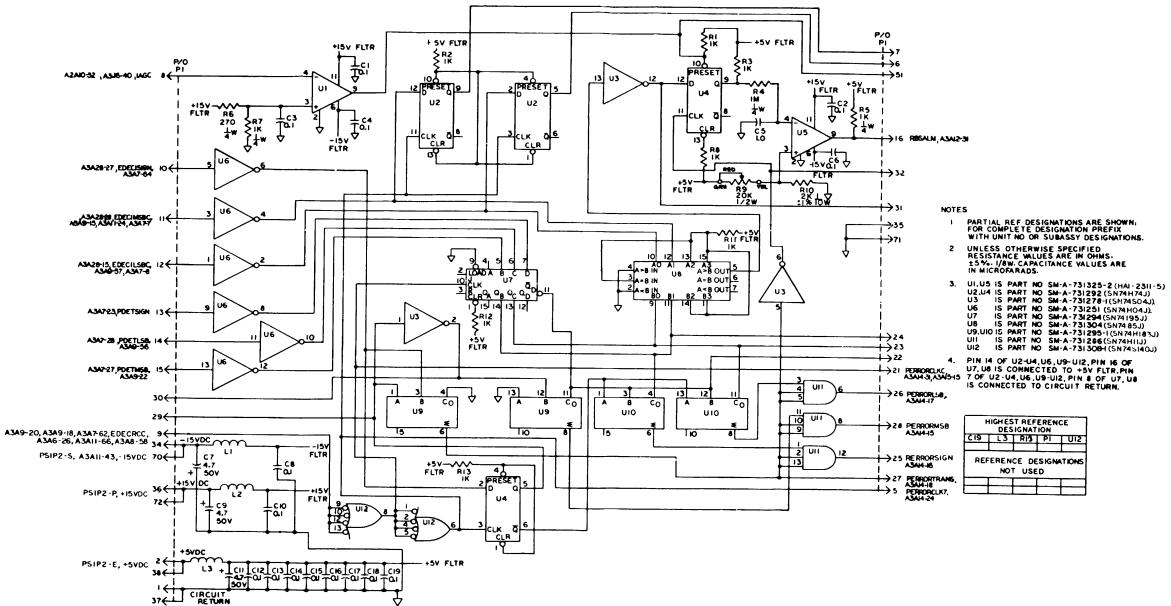

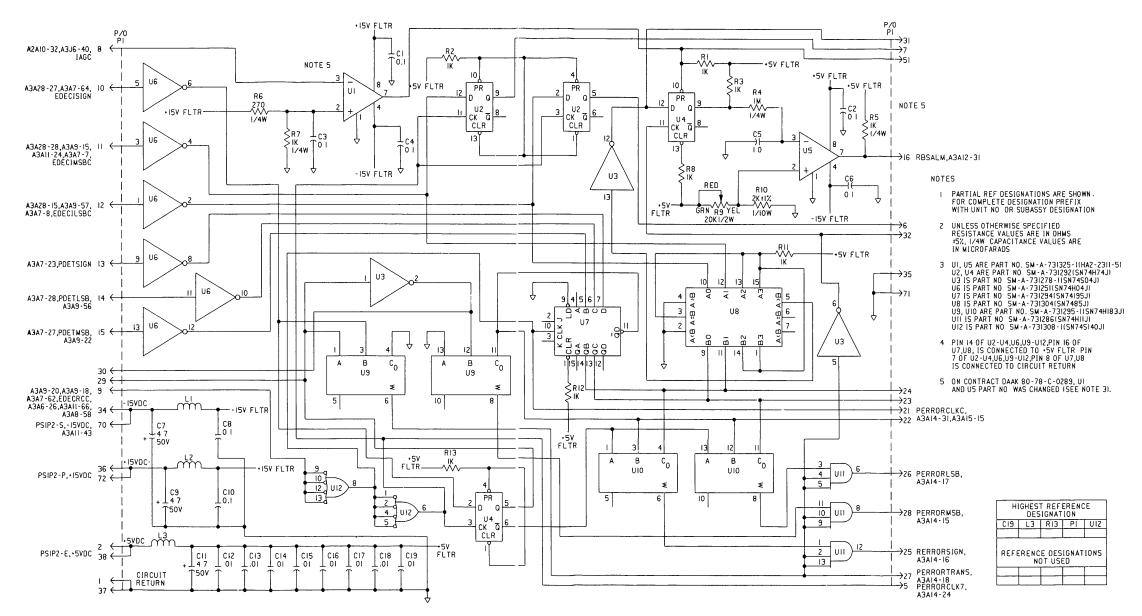

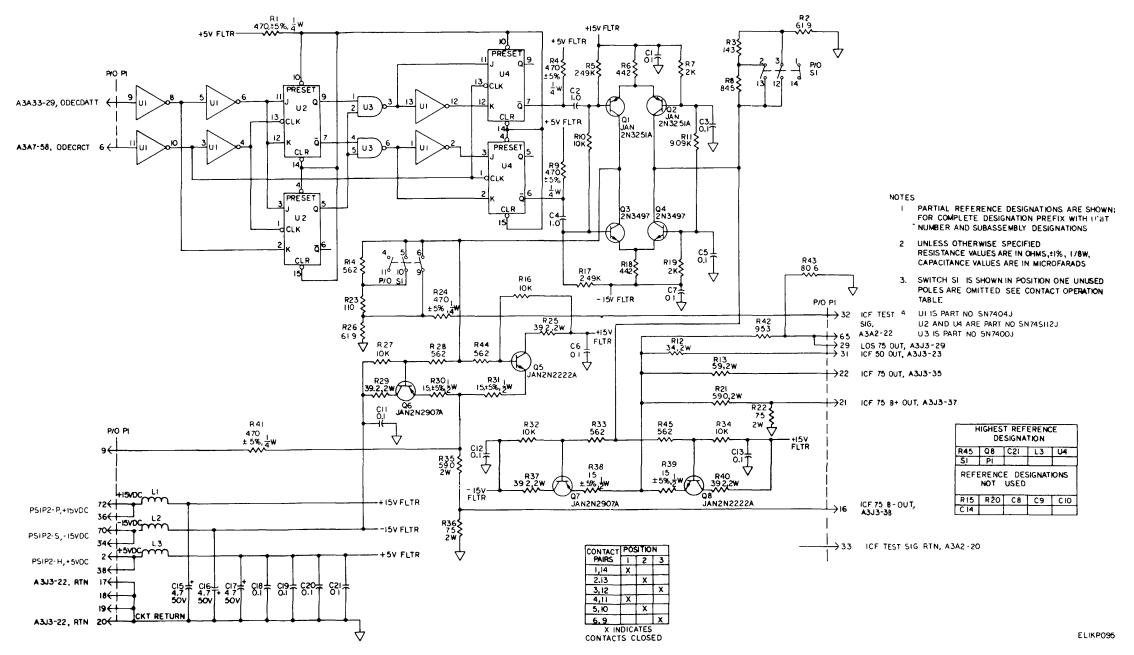

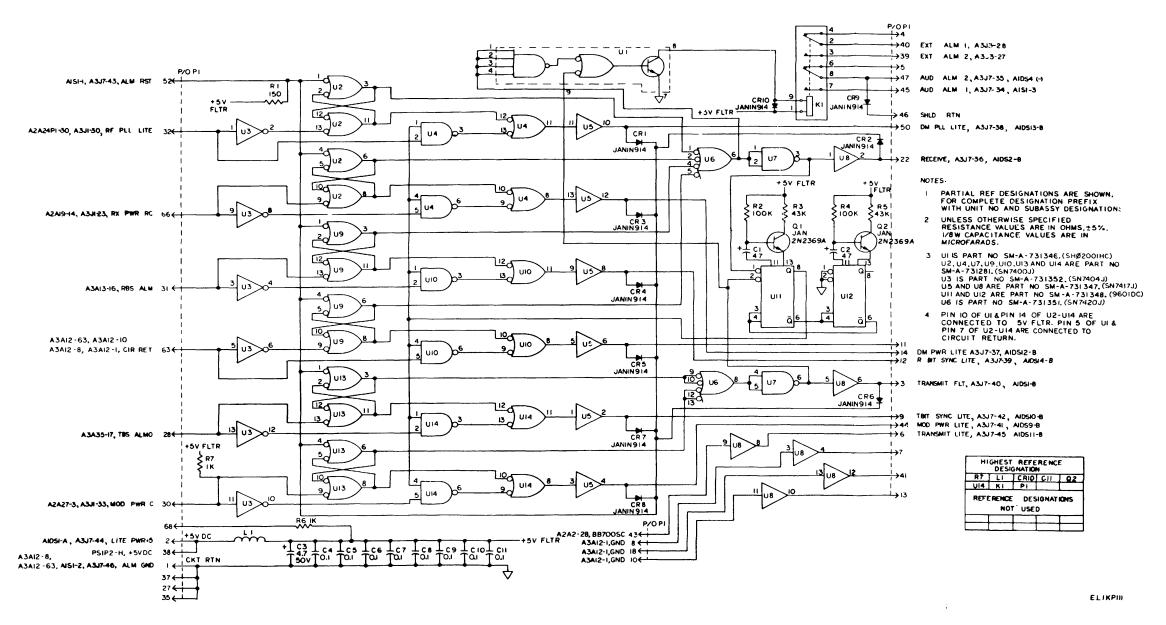

| FO-43<br>  FO-43.1    | Phase and loss of lock detector, A3A13 (SM-D-731225), schematic diagram<br>Phase and loss of lock detector, A3A18 (SM-D-877926), schematic diagram    |              |

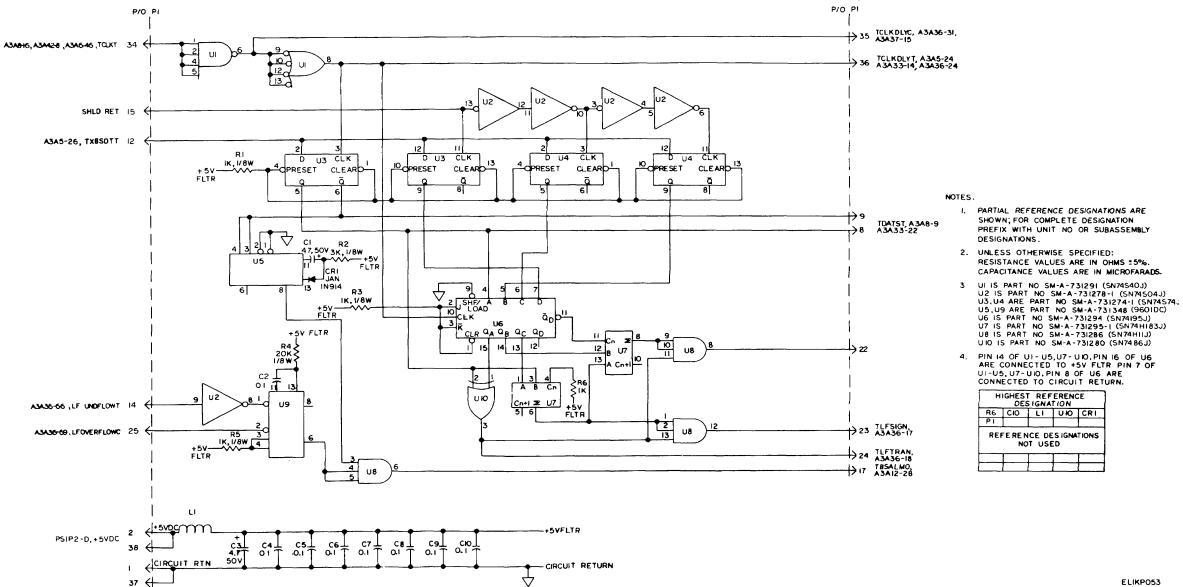

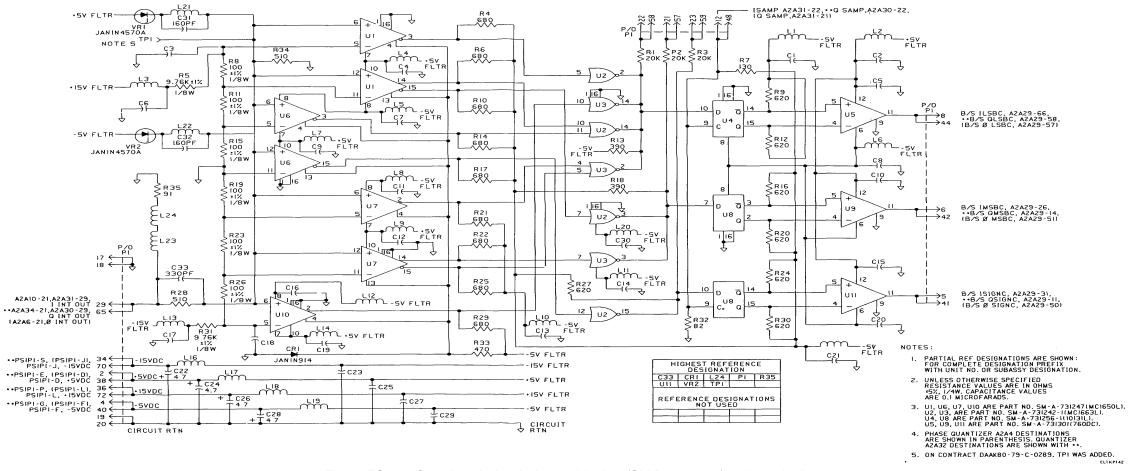

| FO-43.1<br>FO-44      | Timing and automatic gain control, A2A30 and A2A31 (SM-D-731229), schematic diagram                                                                   |              |

| FO-44.1               | Timing and automatic gain control, A2A30 and A2A31 (SM-D-731229), schematic diagram                                                                   |              |

| FO-45                 | Decoder and interface, functional block diagram                                                                                                       |              |

| FO-46                 | Line driver, A3A29, A3A30 and A3A31 (SM-D-742053), schematic diagram                                                                                  |              |

| FO-47                 | cable driver, A3A4 (SM-D-742081) schematic diagram                                                                                                    |              |

| FO-48                 | Stable, clock, A3A39 (SM-D-731201), schematic diagram                                                                                                 |              |

| FO-49                 | Fault and status monitor, functional block diagram                                                                                                    |              |

| FO-50                 | Test circuits, functional block diagram                                                                                                               |              |

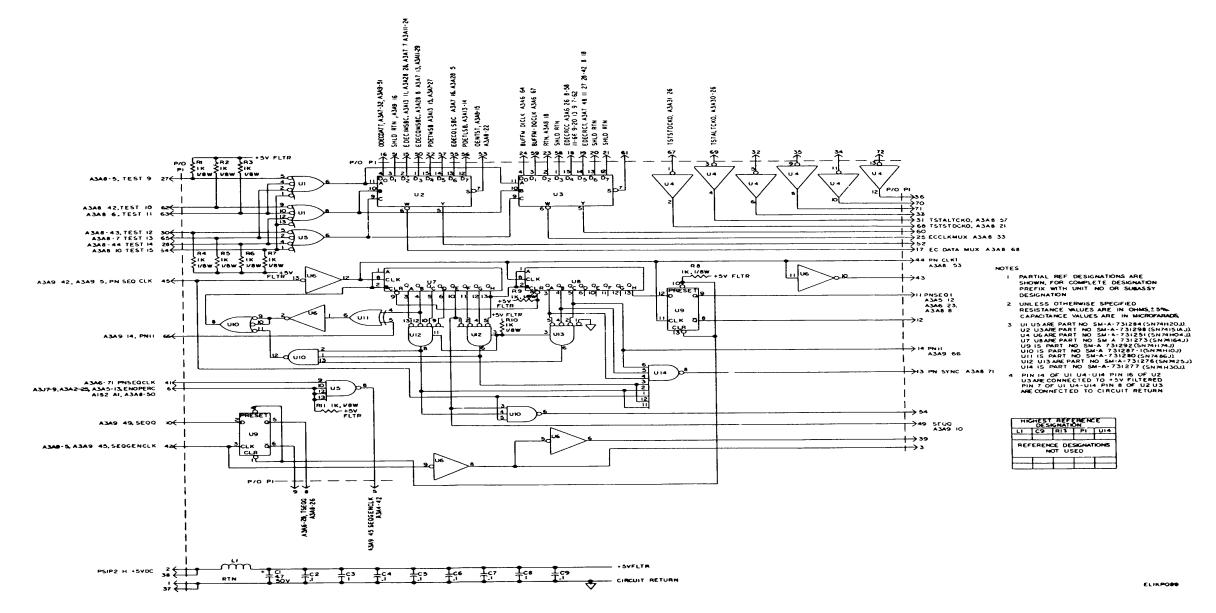

| FO-51                 | 11-bit pseudo-random sequence generator, A3A9 (SM-D-7402057), schematic diagram                                                                       |              |

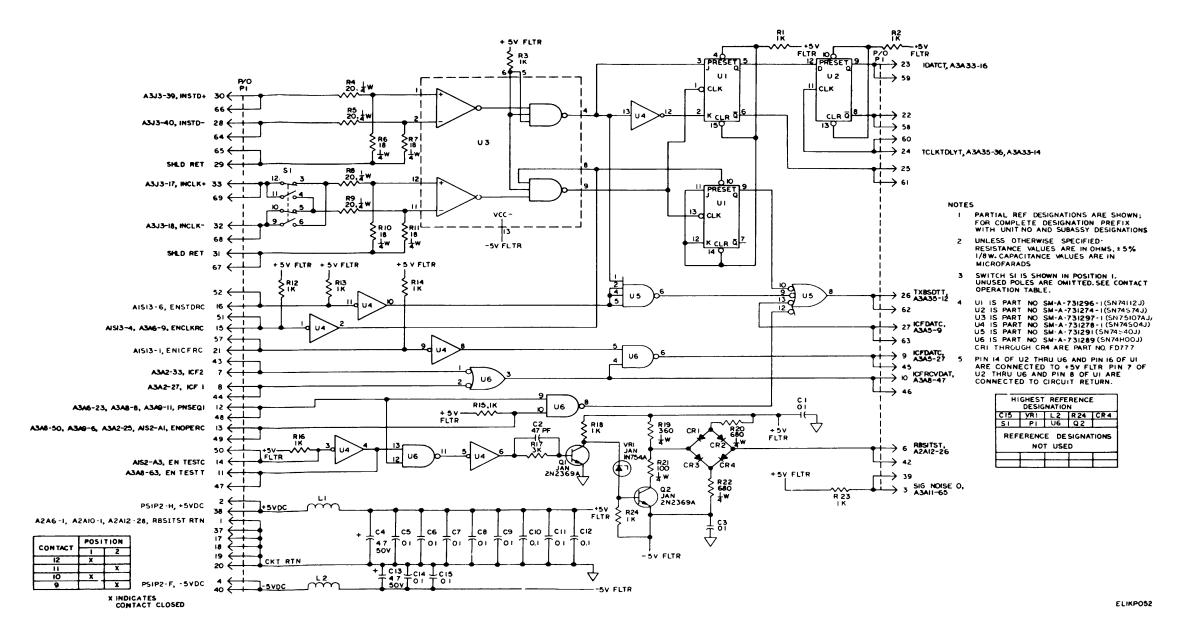

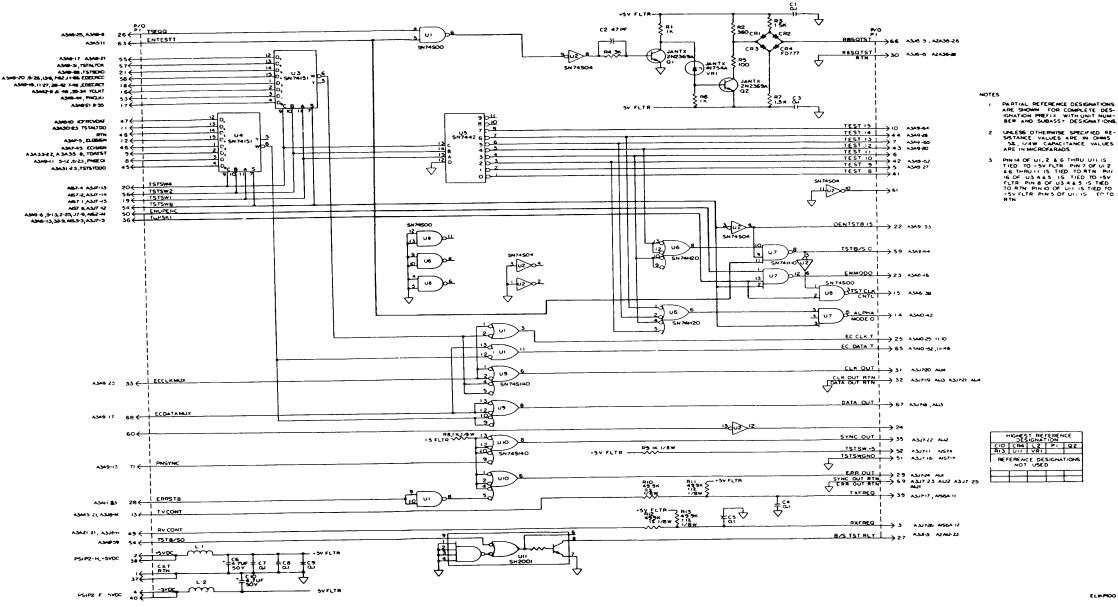

| FO-52                 | Test interface, A3A8 (SM-D-877705), schematic diagram                                                                                                 |              |

| FO-53                 | Error compartor, A3A10 (SM-D-742061), schematic diagram                                                                                               |              |

| FO-54<br>FO-55        | Digital-to-analog meter, A3A11 (SM-D-8777725), schematic diagram<br>Alarm circuit A3A12 (SM-D-742033), schematic diagram                              |              |

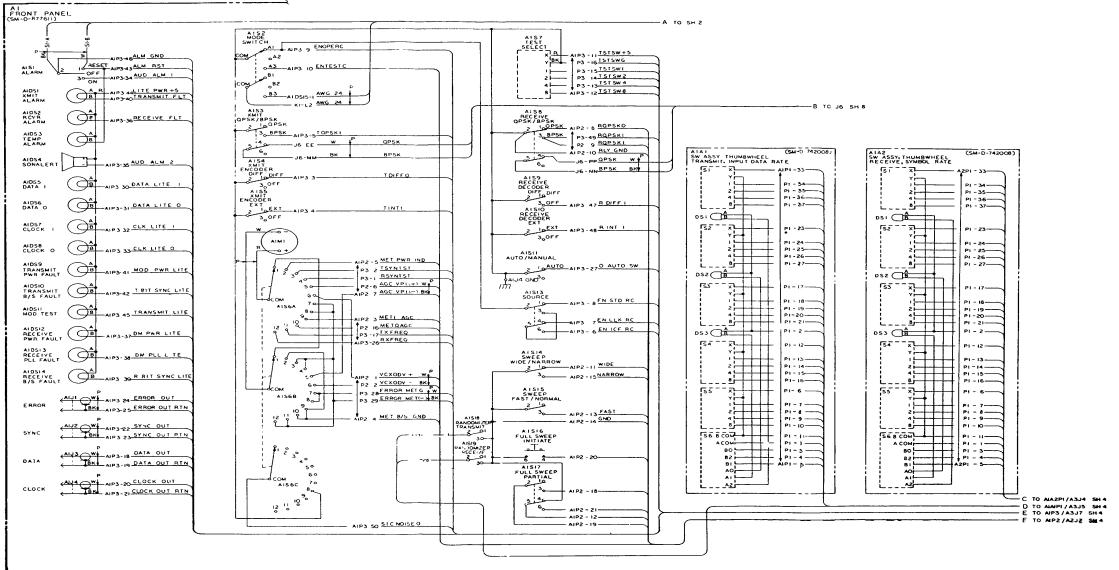

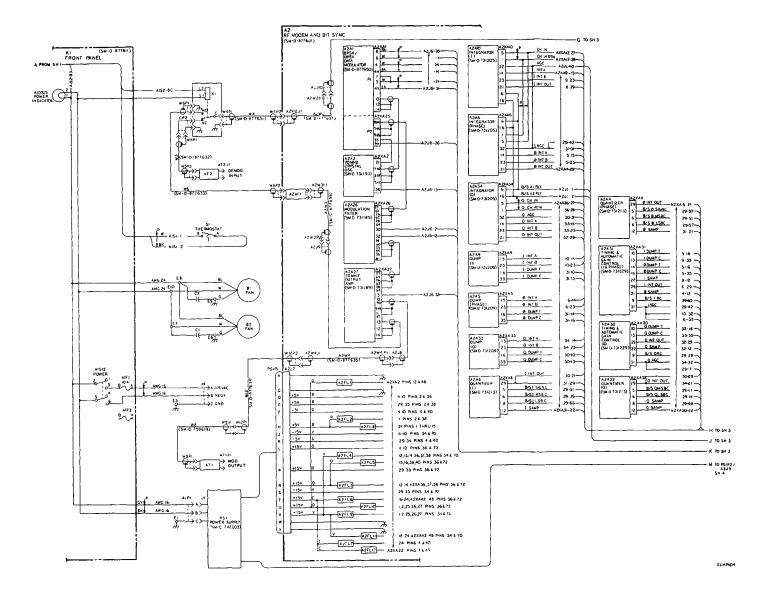

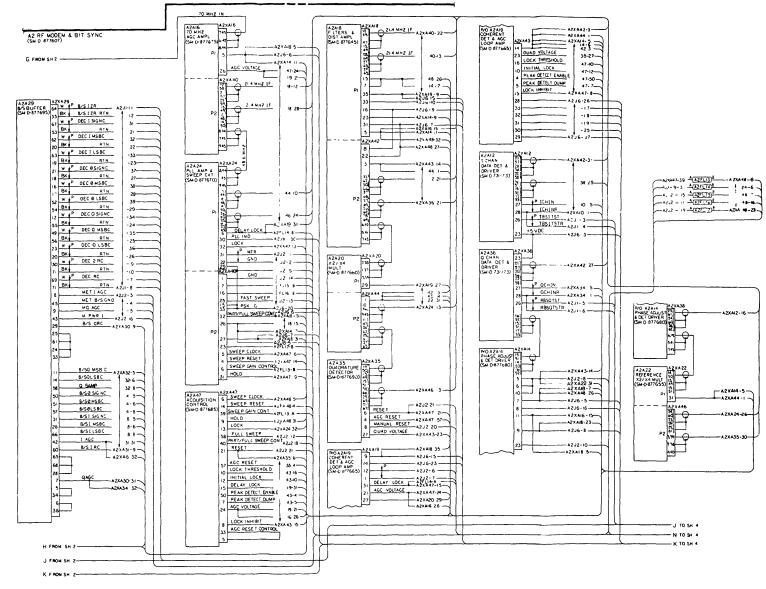

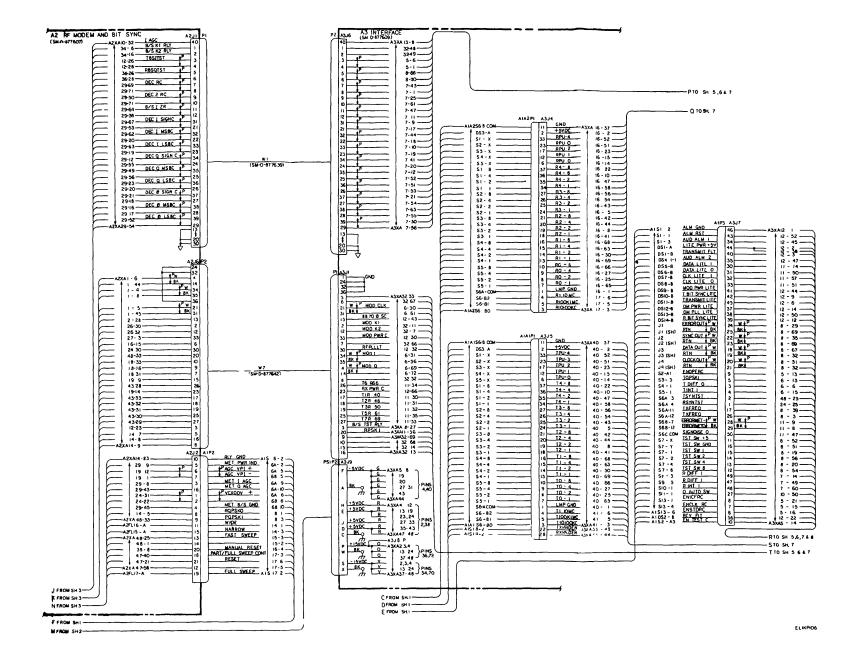

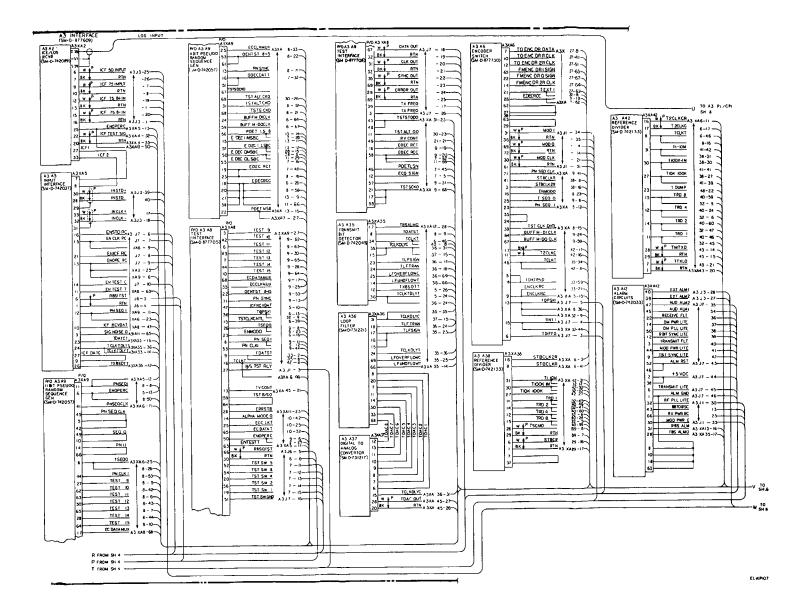

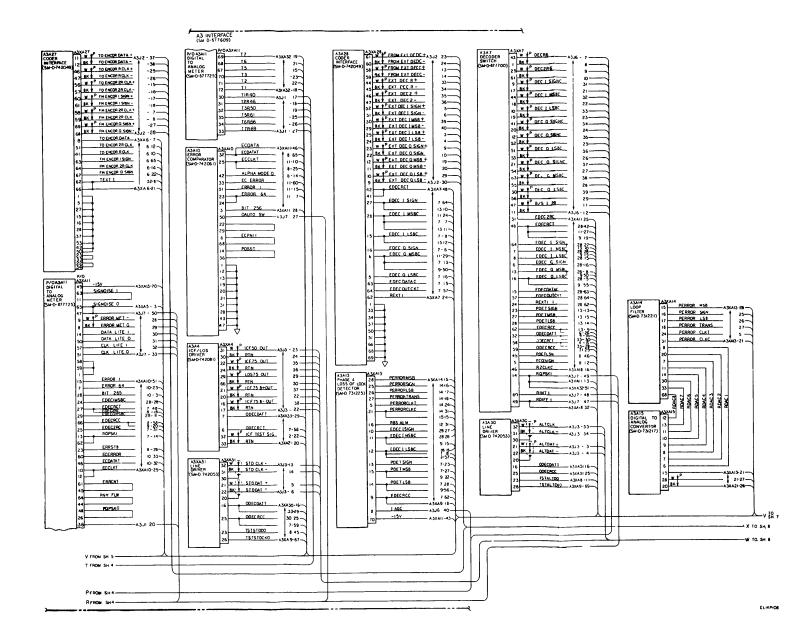

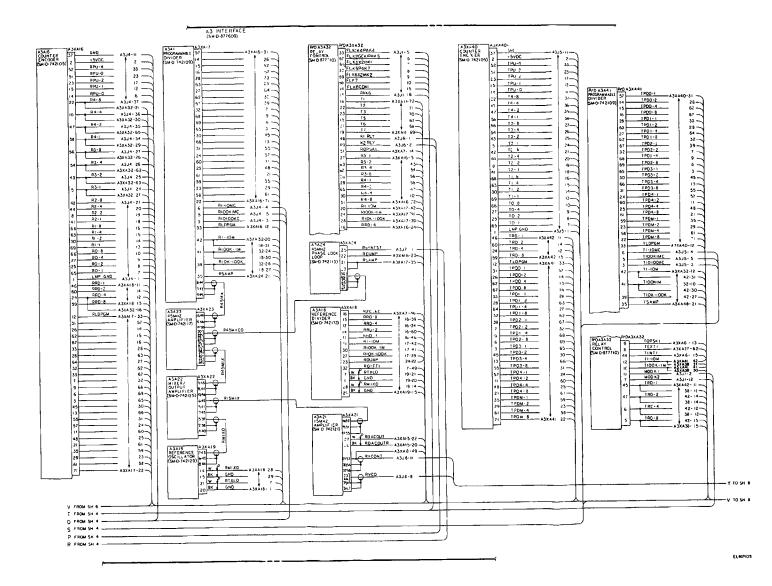

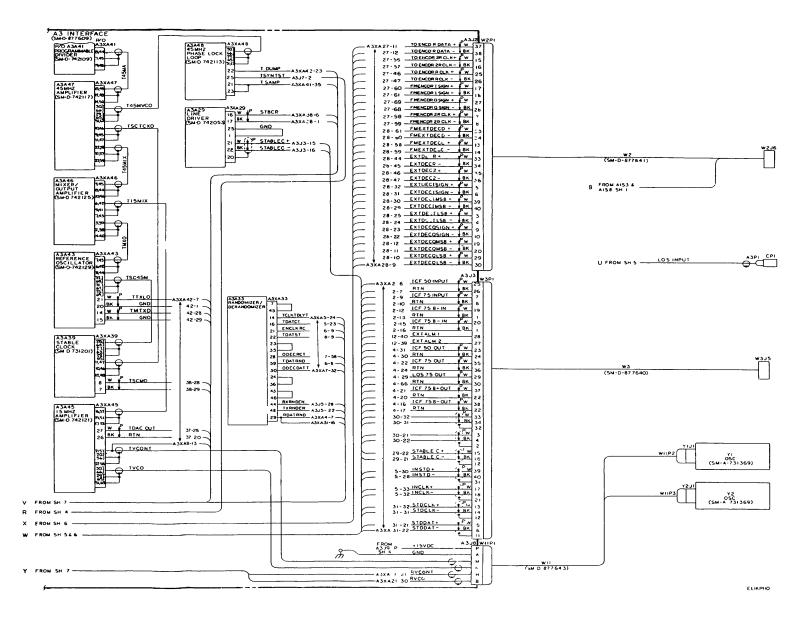

| FO-55<br>FO-56        | QPSK/B PSK connection diagram (8 sheets)                                                                                                              |              |

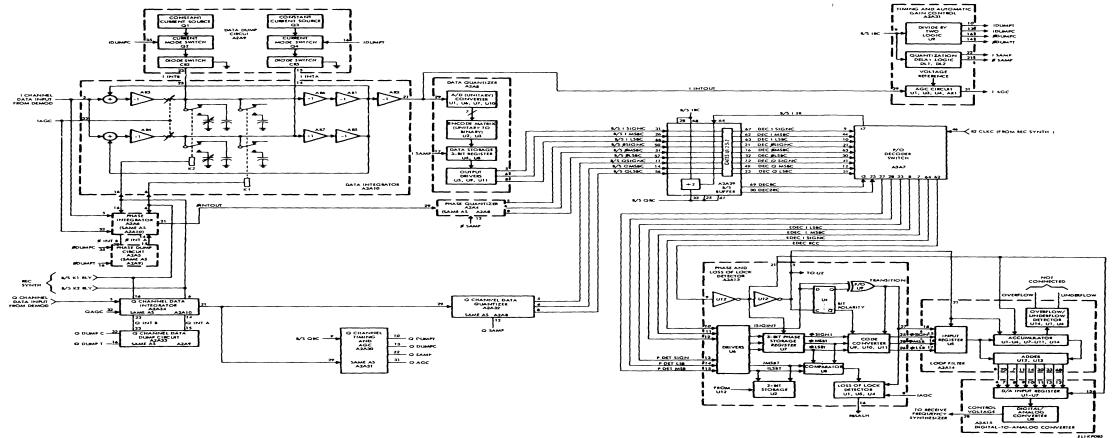

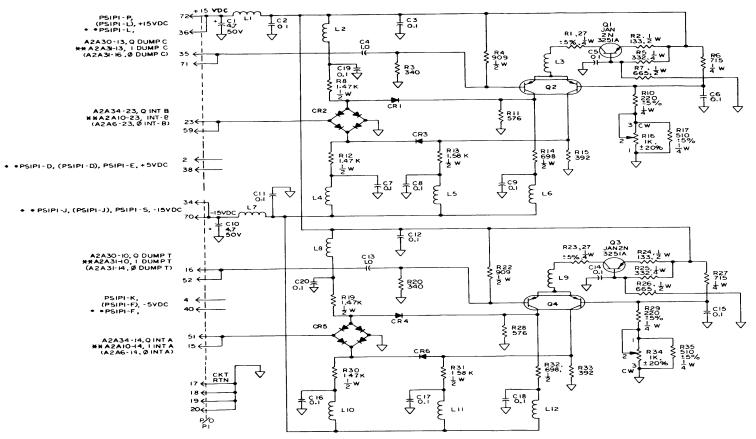

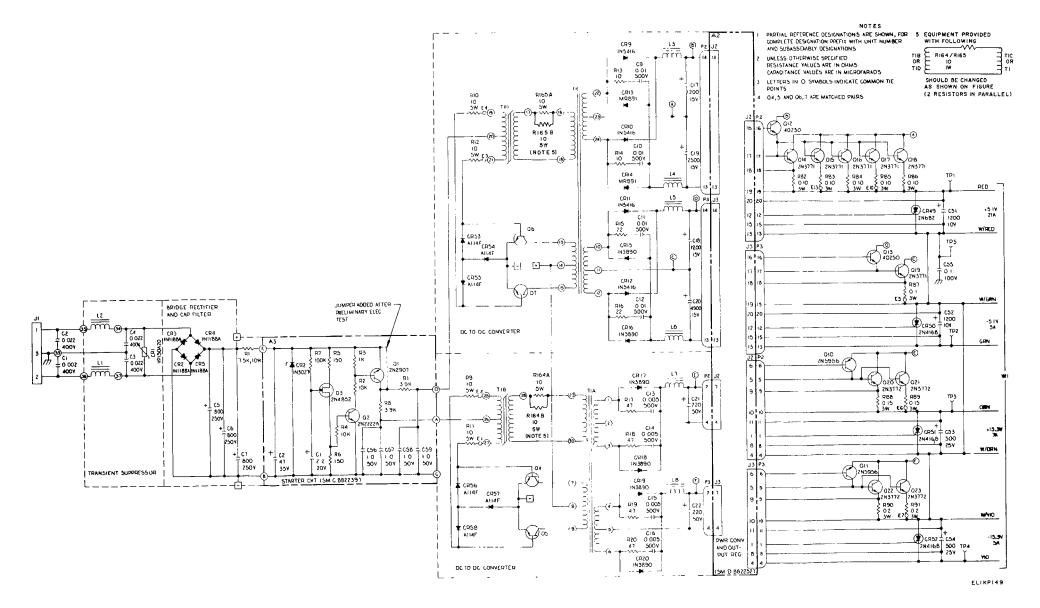

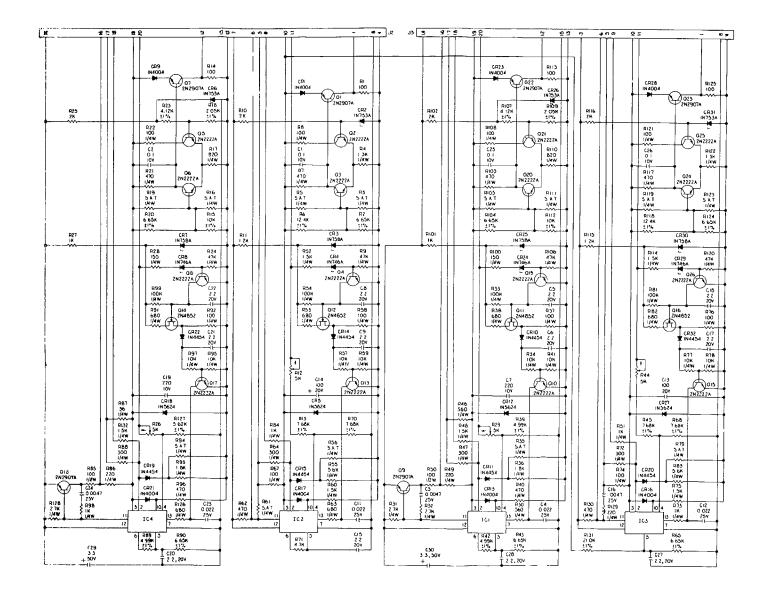

| FO-57                 | Power supply PS1 (SM-C-742003), schematic diagram                                                                                                     |              |

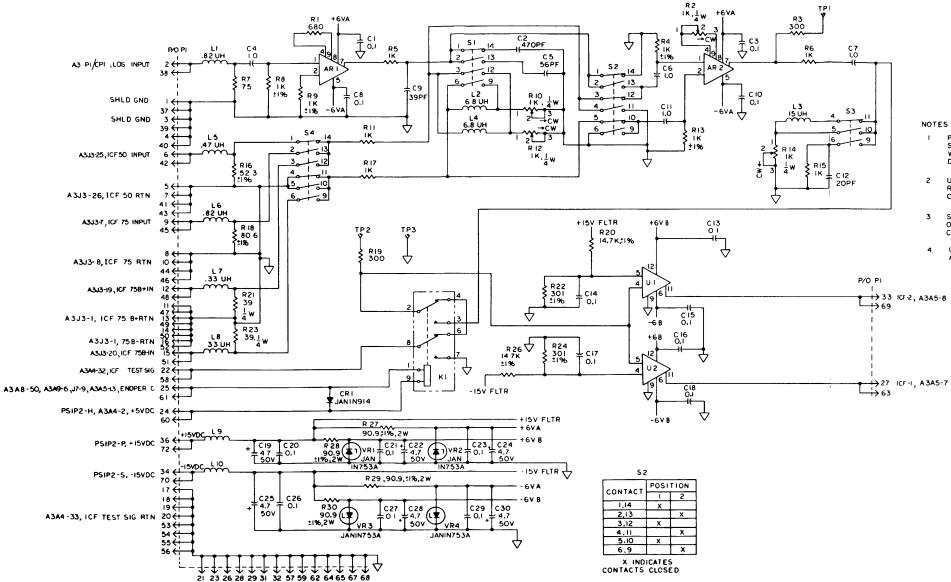

| FO-58                 | Power supply PS1, assembly AI (SM-D-882232), schematic diagram                                                                                        |              |

|                       |                                                                                                                                                       |              |

# TM 11-5820-847-34/NAVELEX 0969-LP-169-5020/TO 31R5-2G-282 LIST OF TABLES

|       | LIST OF TABLES                                                     |      |

|-------|--------------------------------------------------------------------|------|

| Table | Title                                                              | Page |

| 1-1   | Reference designation/FGC cross-reference                          | 1-1  |

| 2-1   | Operation of LOS/cable receiver and decoder selection switches     | 2-6  |

| 2-2   | Phase word format                                                  | 2-11 |

| 2-3   | Synthesizer range selection                                        |      |

| 2-3   | Synthesize ratios and VCO outputs                                  | 2 12 |

|       | Divider ratios and VCO outputs                                     |      |

| 2-5   | Thumb wheel switch coding                                          |      |

| 2-6   | Counter encoder program outputs                                    |      |

| 2-7   | Counter encoder range decoding                                     | 2-20 |

| 2-8   | Multiplier and divider control outputs                             | 2-20 |

| 2-9   | Modulator filter selection                                         |      |

| 2-10  | Bandwidth filtering selection                                      |      |

| 2-11  | Input filter selection                                             |      |

|       |                                                                    |      |

| 2-12  | BPSK filter selection                                              |      |

| 2-13  | QPSK filter selection                                              |      |

| 2-14  | BPSK phase shift selection                                         |      |

| 2-15  | QPSK phase shift selection                                         | 2-39 |

| 2-16  | Relay driver status for BPSK operation                             | 2-40 |

| 2-17  | Relay driver status for QPSK operation                             | 2-41 |

| 2-18  | BPSK relay control signal levels                                   |      |

| 2-19  | QPSK relay control signal levels                                   |      |

| 2-20  | Quantizer unitary to binary conversion                             |      |

| -     |                                                                    |      |

| 2-21  | Phase word code conversion                                         |      |

| 2-22  | Differential decoder configurations                                |      |

| 2-23  | Balanced amplifier drive                                           |      |

| 2-24  | Test switch selections                                             | 2-57 |

| 3-1   | Test equipment required                                            | 3-1  |

| 3-2   | Tools and materials required                                       | 3-1  |

| 3-3   | Operational checks                                                 |      |

| 3-4   | Self-test initial switch settings                                  |      |

| 3-5   | Self-test procedure                                                |      |

|       |                                                                    |      |

| 3-6   | Encoder/decoder test procedure                                     | 3-5  |

| 3-7   | Fault isolation procedure (POWER indicator)                        | 3-6  |

| 3-8   | Fault isolation procedure (ALARM RESET)                            | 3-6  |

| 3-9   | Fault isolation procedure (ALARM RESET OFF)                        | 3-7  |

| 3-10  | Fault isolation procedure (DC PWR)                                 | 3-7  |

| 3-11  | Fault isolation procedure (XMIT SYNTH)                             |      |

| 3-12  | Fault isolation procedure (RCVR SYNTH)                             |      |

| 3-13  | Fault isolation procedure (DEMOD AGC)                              |      |

| 3-14  | Fault isolation procedure (DEMOD XCO)                              |      |

| -     |                                                                    |      |

| 3-15  | Fault isolation procedure (ERROR COUNT 0)                          |      |

| 3-16  | Fault isolation procedure (ERROR COUNT 1)                          |      |

| 3-17  | Fault isolation procedure (ERROR COUNT 2)                          | 3-9  |

| 3-18  | Fault isolation procedure (ERROR COUNTS 3)                         | 3-9  |

| 3-19  | Fault isolation procedure (ERROR COUNT 4)                          | 3-10 |

| 3-20  | Fault isolation procedure (ERROR COUNT 5)                          |      |

| 3-21  | Fault isolation procedure (ERROR COUNT 6)                          |      |

| 3-22  | Fault isolation procedure (ERROR COUNT 7)                          |      |

| 3-23  | Fault isolation procedure (ERROR COUNT 8 or 10 and BIT SYNC AGC I) |      |

| 3-23  | Fault isolation procedure (ERROR COUNT 9 or 11 and BIT SYNC AGC Q) |      |

|       |                                                                    |      |

| 3-25  | Fault isolation procedure (ERROR COUNT 12)                         |      |

| 3-26  | Fault isolation procedure(SIG/NOISE)                               |      |

| 3-27  | Fault isolation procedure(XMIT RATE)                               |      |

| 3-28  | Fault isolation procedure (RCV RATE)                               | 3-13 |

| 3-29  | Fault isolation procedure(momentary ALARM RESET)                   | 3-13 |

| 3-30  | Fault isolation procedure (coder/decoder test)                     | 3-13 |

| 3-31  | Alinement and adjustment following repair action                   |      |

| 3-32  | QPSK/BPSK modem connectors                                         |      |

| 3-32  | Thumbwheel switch, truth table                                     |      |

|       |                                                                    |      |

| 3-34  | Power supply measurements                                          |      |

| 3-35  | Initial control settings for AGC level adjustment.                 |      |

| 3-36  | Initial control settings for post multiplier AGC level adjustment  |      |

| 3-37  | Initial control settings for acquisition threshold adjustment      | 3-27 |

| 3-38  | Deleted                                                            |      |

| 3-39  | Initial control settings for receive bit synchronizer adjustment   | 3-32 |

| 3-40  | Initial control settings for performance testing                   |      |

| 3-41  | Frequency synthesizer rate breakpoints                             |      |

|       |                                                                    |      |

| Fig. No. | Title                                                                       | Page |

|----------|-----------------------------------------------------------------------------|------|

| 3-42     | Modulator data rate breakpoints                                             | 3-50 |

| 3-43     | Demodulator and receive bit synchronizer rate breakpoints                   | 3-50 |

| 3-44     | Performance test failure symptoms, probable causes, and corrective actions  | 3-50 |

| 5-1      | Performance characteristics                                                 |      |

| 5-2      | Load switching and voltage measurements                                     |      |

| 5-3      | Load switching for output ripple measurements                               |      |

| 5-4      | Loss of +5 volt output, troubleshooting procedure                           |      |

| 5-5      | Loss of -5 volt output, troubleshooting procedure                           |      |

| 5-6      | Loss of +15voltoutput, troubleshooting procedure                            |      |

| 5-7      | Loss of - 15 volt output, troubleshooting procedure                         | 5-15 |

| 5-8      | Loss of +5 and -5 volt complementary outputs, troubleshooting procedure     |      |

| 5-9      | Loss of + 15 and - 15 volt complementary outputs, troubleshooting procedure | 5-16 |

| 5-10     | Loss of all power supply outputs, troubleshooting procedure                 |      |

| 5-11     | High output voltage, troubleshooting procedure                              |      |

| 5-12     | All output voltages low, troubleshooting procedure                          |      |

| 5-13     | Low +15 and -15 volt complementary outputs, troubleshooting procedure       | 5-19 |

| 5-14     | Low +5 and -5 volt complementary outputs, troubleshooting procedure         |      |

| 5-15     | Low output voltage-single output, troubleshooting procedure                 |      |

| 5-16     | Output voltage oscillation, troubleshooting procedure                       | 5-20 |

| 5-17     | Excessive line frequency ripple on outputs, troubleshooting procedure       |      |

| 5-18     | Typical resistance measurements                                             |      |

| 5-19     | Typical voltage measurements                                                | 5-22 |

|          |                                                                             |      |

# Change 2 vi

### CHAPTER 1 INTRODUCTION

### 1 - 1. Scope

This manual contains the necessary information for troubleshooting, repair and maintenance of Modem, Digital Data MD-1002/G, hereinafter referred to as the QPSK/BPSK modem. Chapter 2 provides a detailed explanation of circuit operation. Direct support troubleshooting and maintenance procedures for the modem are provided in chapter 3, and chapter 4 provides information for general support maintenance. Chapter 5 provides necessary information for the modem power supply. includina functional description. maintenance, repair, and troubleshooting. Appendix A contains references and appendix B defines mnemonics used on diagrams.

### NOTE

### Refer to TM 38-750 for maintenance forms and records, TM 750-244-2 for destruction of Army electronics materiel

to prevent enemy use, TM 740-90-1 for administrative storage, DA Pam 310-4 for applicable technical manuals, DA Pam 310-7 for current modification work orders, and to TM 11-5820-847-12, paragraph 1-6, for reporting equipment improvement recommendations

### 1 - 2. Equipment Designators

Throughout this manual, assemblies and subassemblies are identified by reference designation; e.g., A2A1, A2A2, etc. These designators are the same as those marked on the equipment. The maintenance allocation chart in TM 11-5820-847-12 and the repair parts and special tools lists in TM 11-5820-847-20P and -34P are, however, organized in functional group code (FGC) sequence. To facilitate use of all equipment documentation, a reference designation to functional group code cross-reference index is provided in table 1-1.

| Reference  | Name                                        | Assembly     | FGC  |

|------------|---------------------------------------------|--------------|------|

| designator |                                             | number       |      |

|            | Modem, Digital Data MD- 1002/ G             | SM-D-877605  | 00   |

| A1         | Control Panel                               | SM-D-877611  | 01   |

| A1A1       | Switch Assembly, Input Data Rate            | SM-D-742008  | 0101 |

| A1A2       | Switch Assembly, I Channel Symbol Rate      | SM-D-742008  | 0102 |

| A2         | RF Modem and Bit Sync Assembly              | SM-D-877607  | 02   |

| A2A1       | QPSK/BPSK Data Receiver and Modulator       | SM-D-877650  | 0201 |

| A2A2       | 70-MHz Oscillator                           | SM-D-731193  | 0202 |

| A2A4       | Quantizer, Phase Channel                    | SM-D-731213  | 0203 |

| A2A5       | Dump Circuit, Phase Channel                 | SM-D-731209  | 0204 |

| A2A6       | Integrator, Phase Channel                   | SM-D-731205  | 0205 |

| A2A8       | Quantizer, I Channel                        | SM -D-731213 | 0206 |

| A2A9       | Dump Circuit, I Channel                     | SM-D-731209  | 0207 |

| A2A10      | Integrator, I Channel                       | SM-D-731205  | 0208 |

| A2A12      | Data Detector and Driver, I Channel         | SM-D-731173  | 0209 |

| A2A14      | Phase Adjust and Detector Driver            | SM-D-877680  | 0210 |

| A2A16      | 70-MHz Gain Control Amplifier               | SM -D-877675 | 0211 |

| A2A18      | Filters and Distribution Amplifier          | SM-D-877645  | 0212 |

| A2A19      | Coherent Detector and AGC Loop Amplifier    | SM-D-877665  | 0213 |

| A2A20      | X2/X4 Multiplier                            | SM-D-877660  | 0214 |

| A2A22      | Reference X2/X4 Multiplier                  | SM-D-877655  | 0215 |

| A2A24      | Phase Lock Loop Amplifier and Sweep Circuit | SM -D-877670 | 0216 |

| A2A26      | Modulation Filter                           | SM-D-731185  | 0217 |

| A2A27      | 70-MHz Output Amplifier                     | SM-D-731189  | 0218 |

| A2A29      | Bit Sync Buffer                             | SM-D-877695  | 0219 |

### Table 1-1. Reference Designation/FGC Cross-Reference

Change 2 1 - 1

# TM 11-5820-847-34/NAVELEX 0969-LP-169-5020/TO 31R5-2G-282 Table 1-1 Reference Designation/FGC Cross-Reference-Continued

| Reference<br>designator | Name                                    | Assembly number            | FGC    |

|-------------------------|-----------------------------------------|----------------------------|--------|

| A2A30                   | Timing and AGC, Q Channel               | SM-D-877930 or SM-D-731229 | 0220   |

| A2A31                   | Timing and AGC, I and Phase Channel     | SM-D-877930 or SM-D-731229 | 0221   |

| A2A32                   | Quantizer, Q Channel                    | SM-D-731213                | 0222   |

| A2A33                   | Dump Circuit, Q Channel                 | SM-D-731209                | 0223   |

| A2A34                   | Integrator, Q Channel                   | SM-D-731205                | 0224   |

| A2A35                   | Quadrature Detector                     | SM-D-877690                | 0225   |

| A2A36                   | .Data Detector and Driver, Q Channel    | SM-D-731173                | 0227   |

| A2A47                   | Acquisition Control                     | SM-D-877935 or SM-D-877685 | 0226   |

| A3                      | Interface and Bit Synchronizer Assembly | SM-D-877609                | 03     |

| A3<br>A3A2              | LOS/Cable Receiver and Decoder          | SM-D-742089                | 0301   |

|                         |                                         |                            |        |

| A3A4                    | LOS/Cable Driver                        | SM-D-742081                | 0302   |

| A3A5                    | Input Interface                         | SM-D-742037                | 0303   |

| A3A6                    | Encoder Switch                          | SM-D-877730                | 0304   |